# VLSI Circuit Reliability under AC Hot-carrier Stress

Kazutaka NOGAMI, Kazuhiro SAWADA, Masaaki KINUGAWA, and Takayasu SAKURAI

Semiconductor Device Engineering Laboratory, TOSHIBA Corp. 1 KomukaiToshiba-cho, Saiwai-ku, Kawasaki, 210 Japan

### Introduction

The hot-carrier problems are one of the most serious obstacles in making high-density, high-speed VLSI with submicron geometry. Consequently, the MOSFET device level degradation under DC and AC stress has been investigated intensively in the past few years. However, little work has been carried out on the circuit level1. This paper deals with two new aspects of the circuit behaviors under AC hot-carrier stress.

One is on a hot-carrier resistant circuit structure called NOEMI (Normally-On Enhancement Mosfet Insertion)2. The verification of the effectiveness of the NOEMI through a direct experiment is carried out for the first time, and the circuit optimization strategy for the NOEMI is described. The other is a proposal of a new simple model which can give insights to the relation between the hot-carrier MOS-FET degradation and the circuit behavior.

## Experiments on NOEMI

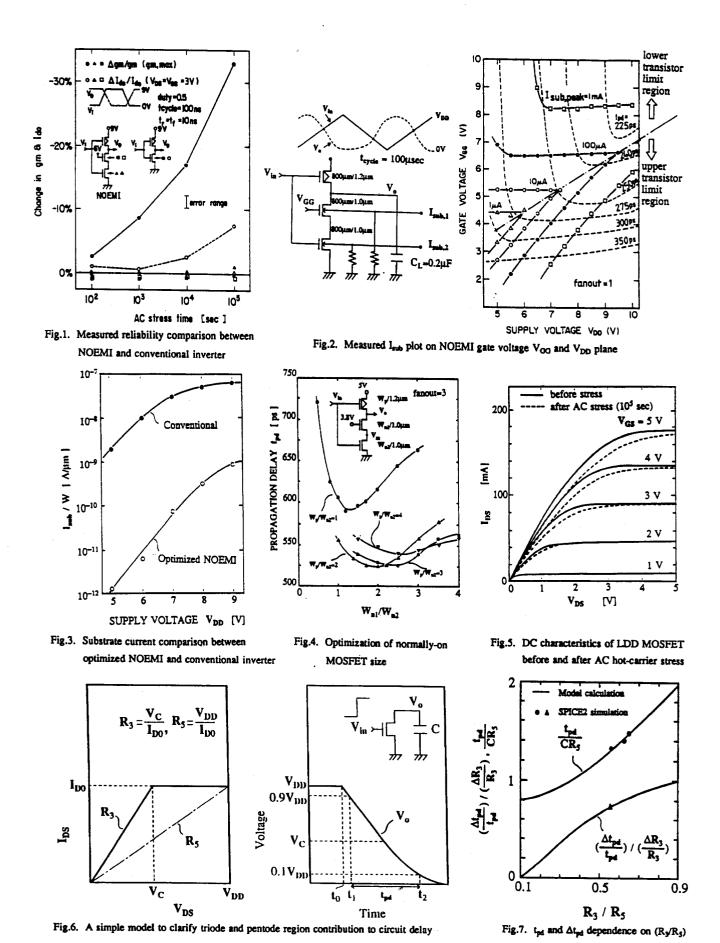

The NOEMI is a circuit structure where serially connected MOSFETs relax drain-source voltage of each MOSFET to suppress hot-carrier generation as shown in Fig.1. The figure demonstrates the NMOSFET hot-carrier degradation comparison between the conventional CMOS inverter and the NOEMI inverter under 9V AC stress. In this experiment, 1µm MLDD NMOS³ and 1.2µm conventional PMOS were used. In the conventional inverter after 105 sec AC stress, the transconductance of the triode region, gm, and the drain saturation current, I40, show degradation more than 30% and 7%, respectively. On the contrary, the NOEMI inverter shows no significant change. It is seen from Fig.1 that the NOEMI has at least three orders of magnitude stronger resistancy to the hot-carrier compared with the conventional inverter. Therefore the NOEMI will be indispensable to assure sufficient reliability for bootstrap circuits in sub-micron DRAMs4, where 8V AC stress is applied even if the supply voltage is 5.5V.

## **NOEMI Optimization**

There are two parameters in the NOEMI structure that should be optimized, namely, the gate voltage( $V_{OO}$ ) and the channel width(W) of the normally-on MOSFET. Vog and the size relate with the reliability and the circuit speed, respectively. Figure 2 shows measured I<sub>mb</sub> plot on V<sub>DO</sub>-V<sub>OO</sub> plane together with simulated propagation delay plot. It is found from Fig.2 that there is an optimum Voc. Voc.or, in terms of reliability when the supply voltage is given, since I<sub>nb</sub> was shown to be a good monitor of the hot-carrier degradation<sup>3</sup>. It is also seen from the figure that the speed remains almost constant even if V<sub>OO</sub> is increased above the optimum point. VOC,OPT is approximately expressed as

$$V_{OO,OPT} \approx \frac{1}{2}V_{DD} + V_{TH}$$

where  $V_{TH}$  denotes the threshold voltage with substrate bias effect. In Fig.3, the I<sub>sub</sub> of the optimized NOEMI in comparison with the conventional inverter is re-plotted to clarify the difference.

Figure 4 shows the relationship between propagation delay and the size of the normally-on MOSFET, (Wal), with the PMOS size(W<sub>p</sub>) as a parameter. When both of W<sub>n1</sub> and W<sub>p</sub> are around  $2W_{n2}$ , the circuit shows the minimum delay. The reason is as follows. If  $W_{n1}$  is small the effective drivability for discharging is small, but if  $W_{n1}$  is too large the junction capacitance of the normally-on MOSFET degrades the speed. Varying  $W_{nl}$  does not affect the reliability because the maximum voltage of the middle node  $V_m$  depends on  $V_{OG}$  but not on  $W_{n1}$ .

# Model for Circuit Degradation

Figure 5 shows the typical DC characteristics of 1µm MLDD NMOS before and after AC hot-carrier stress. The device shows the degradation especially in a triode region, being same as the DC stress degradation. How does this LDD type of degradation affect the circuit speed? In order to understand the relationship between the triode region degradation and circuit delay, a simple model as shown in Fig.6 is proposed. The advantage of this model is the freedom of varying triode and pentode characteristics independently. R3 and R<sub>5</sub> signify the effective MOSFET resistance in the triode region and in the pentode region, respectively. With this model the switching delay tpd is expressed as follows.

$$\frac{t_{pd}}{CR_5} = 0.9 + \frac{R_3}{R_5} \ln \frac{10R_3}{eR_5}$$

If R<sub>3</sub> is changed from R<sub>3</sub> to R<sub>3</sub>+ $\Delta$ R<sub>3</sub> due to the hot-carrier effects, the change in  $t_{pd}$ ,  $\Delta t_{pd}$ , is expressed as

$$(\frac{\Delta t_{pd}}{t_{pd}}) \ / \ (\frac{\Delta R_3}{R_3}) \ = \ \frac{(R_3/R_5) \ ln(10R_3/R_5)}{0.9 + (R_3/R_5) \ ln(10R_3/eR_5)}$$

The above model calculation agrees well with the SPICE2 simulation using AC hot-carrier degraded MOSFETs as shown in Fig.7. The figure suggests that the change rate of  $t_{pd}$  is small when  $R_3/R_3$  is small. The R<sub>3</sub>/R<sub>3</sub> decreases for smaller MOSFETs because of the velocity saturation of carriers by gate voltage. As a result, even if 10% change is observed in  $\Delta R_3/R_3$  by the hot-carrier degradation, the circuit speed becomes less sensitive to the hot-carrier degradation for smaller MOSFETs.

## Conclusions

The NOEMI circuit technology is experimentally shown to be effective in realizing reliable sub-micron VLSIs, and found to have the optimized gate voltage and the optimized size for the normallyon MOSFET. Secondly, a simple model is proposed which helps to understand the relationship between the LDD MOSFET degradation and the circuit degradation.

## Acknowledgement

The authors wish to thank M.Matsui, K.Kakumu, T.Iizuka, O.Ozawa and Y.Unno for encouragement and discussions. They also thank T.Shirotori and Y.Ito for supports.

#### References

- Horiuchi T. et al., "Hot-Carrier Induced Degradation of N-MOSFETs in Inverter Operation," Symp. on VLSI Tech., pp.104-105, 1985.

Sakurai T. et al., "Hot-Carrier Generation in Submicron VLSI Environ-

- ment", IEEE, J.SSC, SC-21, pp.187-192, Feb.1986.

- 3) Kinugawa M. et al., "Submicron MLDD NMOSFETs for 5V Operation," Symp. on VLSI Tech., pp.116-117, 1985.

- Sakurai T. et al., "A 1Mb Virtually Static RAM," IEEE ISSCC, Dig. of Tech. Papers, pp.252-253, Feb.1986.

- Takeda E. et al., "Hot-Carrier Effects in Submicron VLSIs," 1983 Symp. on VLSI Tech., p.104, 1983.