# CMOS INVERTER DELAY AND OTHER FORMULAS USING a-POWER LAW MOS MODEL

Takayasu Sakurai

Reprinted from PROCE**DINGS OF THE IEEE INTERNATIONAL**CONFERENCE **ON COMPUTER-AIDED DESIGN**Santa Clara, **CA, November 7-10**, 1988

A A STANISH STANISH

## CMOS Inverter Delay and Other Formulas Using α-Power Law MOS Model

### Takayasu SAKURAI

Semiconductor Device Engineering Laboratory Toshiba Corporation, Kawasaki, 210 Japan

#### **Abstract**

Simple yet realistic MOS model, namely  $\alpha$ -power law MOS model, is introduced to include carrier velocity saturation effect which becomes eminent in short-channel MOSFETs. The model is an extension of Shockley's square law MOS model in the saturation region. Using the model, closed-form expressions are derived for delay, short-circuit power, and transition voltage of CMOS inverters. The resultant delay expression includes input waveform slope effects and parasitic drain/source resistance effects and can be used in simulation and/or optimization CAD tools. It is concluded that the CMOS inverter delay becomes less sensitive to the input waveform slope and short-circuit dissipation increases as MOSFETs becomes small.

#### Introduction

An expression for CMOS inverter delay was first introduced by J.R.Burns[1]. However, the MOSFET model used in the theory was Shockley's simple formula which can not reproduce voltage-current characteristics of the recent short-channel MOSFETs. Moreover, Burns's expression does not include input waveform slope effect and source/drain resistance effect. The source/drain resistance effect is important in estimating delay degradation by parasitic diffusion resistance of MOSFETs and hot-carrier degradation effect in circuit level[2,3]. Hedenstierna and Jeppson take into account the input waveform slope effect on inverter delay[4], but the theory is also based on Shockley model.

In considering these points, a new MOS model is introduced. Although the model is simple and can be treated analytically, it reproduces the short-channel MOSFET characteristics better than Shockley model. Using the model, closed-form expressions are derived for delay, short-circuit power, and transition voltage of CMOS inverters.

#### Simple Short-Channel MOSFET Model

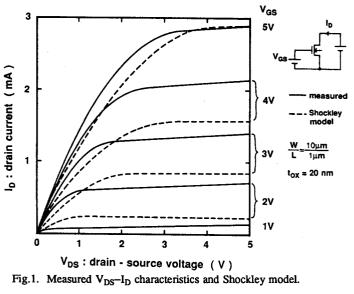

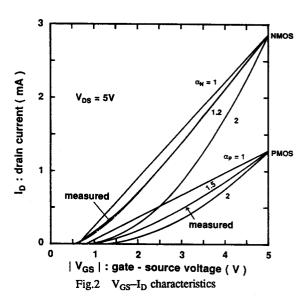

Figure 1 shows a comparison between Shockley model and measured MOSFET  $V_{DS}-I_D$  characteristics for 1µm NMOS transistor. It is clear that Shockley model fails to reproduce the I-V characteristics of the recent MOSFET. The biggest discrepancy comes from neglect of velocity saturation effect of carriers[5]. Figure 2 shows  $V_{GS}-I_D$  characteristics in the saturation region. As seen from Fig.2, drain current  $I_D$  is proportional to  $(V_{GS}-V_{TH})^\alpha$ . Shockley model claims that  $\alpha\!=\!2$ , whereas the measured value of  $\alpha$  for around 1 µm rule is 1.2 for N-channel MOSFET and 1.5 for P-channel MOSFET because of the velocity saturation by gate-source voltage  $V_{GS}$ .

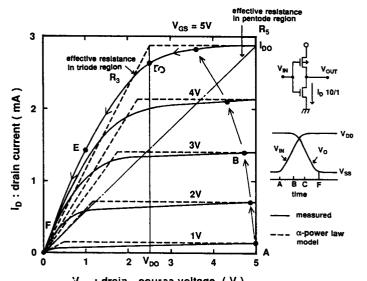

Taking the above discussion into account,  $\alpha$ -power law model as seen in Fig.3 is proposed. The model is based on four parameters,  $V_{TH}$  (threshold voltage),  $I_{D0}$  (drain current at  $V_{GS}=V_{DS}=V_{DD}$ ),  $V_{D0}$  (drain saturation voltage at  $V_{GS}=V_{DD}$ ), and  $\alpha$  (velocity saturation parameter). All these parameters are easily obtained from measured data, and especially  $I_{D0}$  is a good index of the drivability of MOSFETs and frequently used by VLSI designers. The model equations are given below.

$$I_D = \begin{cases} 0 & (V_{GS} \le V_{TH} : \text{cut-off region}) \\ (I_{D0}'/V_{D0}')V_{DS} & (V_{DS} < V_{D0}' : \text{triode region}) \\ I_{D0}' & (V_{DS} \ge V_{D0}' : \text{pentode region}) \end{cases}$$

Eqs. 1

.where

$$I_{D0}' = I_{D0} \left[ \frac{V_{GS} - V_{TH}}{V_{DD} - V_{TH}} \right]^{\alpha}, \ V_{D0}' = V_{D0} \left[ \frac{V_{GS} - V_{TH}}{V_{DD} - V_{TH}} \right]^{\alpha/2}$$

Eqs.2

#### Input Waveform Slope and Delay

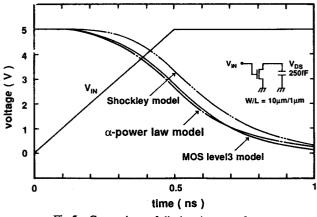

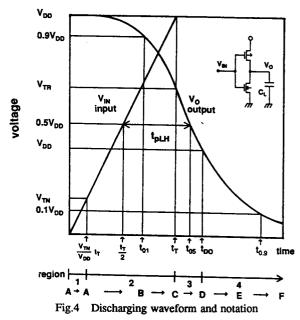

By using the  $\alpha$ -power law model, an expression for the delay is derived. First consider the case of discharging the output capacitance with NMOS as shown in Fig.4, where the input voltage is varied linearly in transient time of  $t_T$ . In this case, the effect of PMOS can be neglected as is pointed out by Ref.[4]. Figure 5 shows a comparison of the delay calculated using SPICE MOS level 3 model[6], the  $\alpha$ -power law model and the Shockley model. Better agreement is shown between SPICE and the proposed model. After the conventional manipulation of differential equations, the delay,  $t_{pHL}$  and  $t_{pLH}$  can be expressed as follows.

$$t_{pHL},\,t_{pLH} = \left[\frac{V_{TH}/V_{DD} + \alpha}{1+\alpha} - \frac{1}{2}\right]t_T + \frac{C_LV_{DD}}{2I_{D0}} \qquad \text{Eq.3}$$

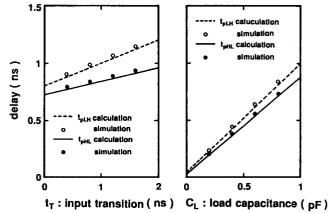

In the above expression, the first term is the input dependent term which is linearly dependent on the input slope  $t_T$ , and the second term is the output capacitance dependent term. This expression is independent of the triode region model of Eqs.1 and 2, when  $V_{D0}$  is near or less than half  $V_{DD}$ , which is typical. A comparison is made in Fig.6 between SPICE simulation and calculation with the above formula.

It is interesting to note that the delay becomes less sensitive to the input slope when MOSFET becomes miniaturized and  $\alpha$  becomes smaller, because the factor (V<sub>TH</sub>/V<sub>DD</sub> +  $\alpha$ ) / (1 +  $\alpha$ ) – 1/2 decreases monotonously as  $\alpha$  decreases. This is assured by Fig.6, where  $\alpha$  for NMOS (t<sub>pHL</sub>) is 1.2 and  $\alpha$  for PMOS (t<sub>pLH</sub>) is 1.5.

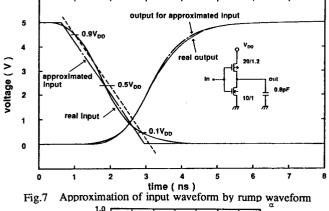

Next step is to approximate the real input waveform by a rumped waveform to obtain effective  $t_T$ . As seen from Fig.7, good approximation is achieved by connecting  $0.1V_{DD}$  point and

$V_{\text{DS}}$  : drain - source voltage ( V ) Fig.3 Proposed α-power law MOS model

Fig.5 Comparison of discharging waveforms

Fig.6 Calculated and simulated value for  $t_{pLH}$  and  $t_{pHL}$

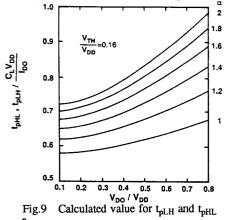

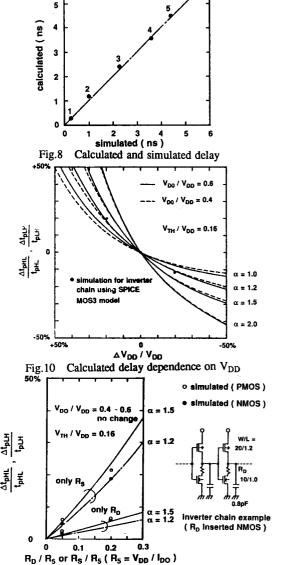

$0.9V_{DD}$  point, when the input slope is similar to the output slope, which is often met in real VLSIs. Using this approximation, the delay estimation is carried out for the circuit of Fig.8(a), together with the result in Fig.8(b). Using the same assumption,  $t_T$  is expressed as follow, and the normalized delay calculated by this formula is plotted in Fig.9.

$$t_T = \frac{t_{0.9} - t_{0.1}}{0.8} = \frac{C_L V_{DD}}{I_{D0}} \left[ \frac{0.9}{0.8} + \frac{V_{D0}}{0.8 V_{DD}} \ln \frac{10 V_{D0}}{e V_{DD}} \right] \quad \text{Eq.4}$$

If it is assumed that  $V_{D0}/V_{DD}$ =0.5 and  $\alpha$ =1.5, which is typical, the delay of Eq.3 is simplified as 0.75C<sub>L</sub>R<sub>5</sub> using Eq.4, where R<sub>5</sub> ( $\equiv V_{DD}/I_{D0}$ ) is an effective pentode resistance of MOSFET as shown in Fig.3.

Figure 10 shows the delay variation with  $V_{DD}$ , using the  $\alpha$ -power law MOS model. It is seen that the delay dependence on  $V_{DD}$  gets milder when the velocity saturation gets worse, that is,  $\alpha$  tends to 1.

#### Effect of Source and Drain Resistance on Delay

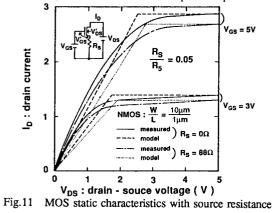

Figure 11 is static characteristics of MOSFETs with drain resistance  $R_D$  or source resistance  $R_S$ . In order to include the source/drain resistance effect, only the following substitutions are to be made. Then, the above discussions and expressions are all valid. These substitutions are easily derived from Eqs.1 and 2.

$$\begin{split} I_{D0} \to I_{D0} / \left[ 1 + \frac{\alpha}{1 - V_{TH} / V_{DD}} \cdot \frac{R_S^{'}}{R_5} \right], \\ \frac{V_{D0}}{V_{DD}} \to \frac{V_{D0}}{V_{DD}} + \frac{R_D}{R_5} + \frac{R_S}{R_5} \end{split}$$

Eqs.5

Figure 12 shows a comparison between the calculation by the formula and SPICE simulation. The inverter delay with the resistance inserted turns out to be approximated as follows for around 1µm MOSFETs.

$$\frac{\Delta t_{\text{pHL}}}{t_{\text{pHL}}}$$

,  $\frac{\Delta t_{\text{pLH}}}{t_{\text{pLH}}} \approx \frac{R_{\text{S}}}{R_{\text{5}}} + \frac{1}{3} \frac{R_{\text{D}}}{R_{\text{5}}} \approx \frac{1}{2} \frac{R_{\text{S}}}{R_{\text{3}}} + \frac{1}{6} \frac{R_{\text{D}}}{R_{\text{3}}}$  Eq.6

,where  $R_3$  ( $\equiv V_{D0}/I_{D0}$ ) denotes an effective triode resistance of MOSFET. If the resistance is inserted only in series with the NMOS and not with PMOS, then the inverter-chain delay degradation is about a half of the above formula.

#### Short-Circuit Power in Static CMOS Circuit

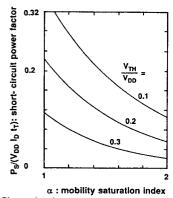

There is a direct current path in a CMOS inverter when both of the NMOS and PMOS are on. The expression of the power consumed in this mode is first given by Veendrick[7], based on Shockley model. By replacing the MOS model from Shockley model to the  $\alpha$ -power law model, the short-circuit power consumed per one switching,  $P_S$ , is expressed as follows.

$$\begin{split} P_{S} &= 2 \cdot V_{DD} \cdot 2 \int_{0}^{t_{T}/2} I_{D}(V_{GS} = V_{DD} \ t \ / \ t_{T}) \ dt \\ &= V_{DD} \ t_{T} \ I_{D0} \ \frac{1}{\alpha + 1} \frac{1}{2^{\alpha - 1}} \frac{(1 - 2 \ V_{TH}/V_{DD})^{\alpha + 1}}{(1 - V_{TH}/V_{DD})^{\alpha}} \end{split}$$

Eq.7

If  $\alpha$  is set to 2 as in Shockley model, this formula is reduced to Veendrick's formula. The result is not dependent on the triode model. The plot of the formula is given in Fig.13. It is seen that the short-circuit dissipation component increases as MOSFETs become smaller and the velocity saturation index  $\alpha$  decreases to unity.

#### Transition Voltage

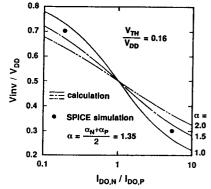

The logic transition voltage, or inverting voltage[8] of a CMOS inverter can also be calculated by the  $\alpha$ -power law model. Equating drain current of PMOS and NMOS in the pentode region, the following formula is derived for the transition voltage, Vinv, with an assumption that the threshold voltage of PMOS and NMOS is equal to  $V_{TH}$  and the PMOS and NMOS have the same  $\alpha$ .

$$\frac{V_{inv}}{V_{DD}} = \frac{\left(I_{D0,N} / I_{D0,P}\right)^{1/\alpha} \left(V_{TH} / V_{DD}\right) + \left(1 - V_{TH} / V_{DD}\right)}{\left(I_{D0,N} / I_{D0,P}\right)^{1/\alpha} + 1} \frac{Eq.8}{Eq.8}$$

,where  $I_{D0,P}$  and  $I_{D0,N}$  stand for  $I_{D0}$  of PMOS and NMOS, respectively. The result is graphically shown in Fig.14, indicating that Shockley model, where  $\alpha$  is set to 2, is not a good approximation in estimating the transition voltage. It is seen that as  $\alpha$  becomes small, the transition voltage becomes more sensitive to the gate width ratio of PMOS and NMOS, that is,  $I_{D0,P}$  /  $I_{D0,N}$ . This result is not dependent on the triode model.

#### Summary

Useful delay, power and transition voltage expressions are derived with a new MOSFET model, which can be used for CAD tools. It is shown that as MOSFETs get miniaturized, the CMOS inverter delay becomes less sensitive to the input waveform slope, and to the  $V_{\rm DD}$  variation. In addition, short-circuit dissipation increases, and transition voltage becomes more sensitive to the gate width ratio of PMOS and NMOS.

Further extension is preferable for triode region characteristics modeling to increase precision, although the results obtained here remain essentially unchanged. It is because all formulas except Eqs.4 and 5 do not depend on the triode model. Since the proposed model efficiently models the short-channel MOSFET, it can be used to modify the classical expressions based on Shockley model. One interesting application is on a CMOS arbiter optimization[5].

#### References

- J.R.Burns, "Switching Response of Complementary-Symmetry MOS Transistor Logic Circuits," RCA Rev., 25, pp.627-661, Dec.1964.

- [2] T.Sakurai, K.Nogami, M.Kakumu, & T.Iizuka, "Hot-Carrier Generation in Submicrometer VLSI Environment," IEEE J. Solid State Circ., SC-21, No.1, pp.187-192, Feb.1986.

- [3] K.Nogami, K.Sawada, M.Kinugawa, & T.Sakurai, "VLSI Circuit Reliability under AC Hot-Carrier Stress," Symp. on VLSI Circuits, pp.13-14, May 1987.

- [4] N.Hedenstierna & K.O.Jeppson, "CMOS Circuit Speed and Buffer Optimization," IEEE Trans. on CAD, CAD-6, No.2, pp.270-280, Mar.1987.

- [5] T.Sakurai, "Optimization of CMOS Arbiter and Synchronizer with Sub-micron MOSFETs," IEEE J. Solid State Circuits, SC-23, No.4, pp.901-906, Aug.1988.

- [6] A.Vladimirescu, & S.Liu, "The Simulation of MOS Integrated Circuits Using SPICE2," U.C.Berkeley ERL Memo, No.M80/7, Oct.1980.

- [7] H.Veendrick, "Short-Circuit Dissipation of Static CMOS Circuitry and Its Impact on the Design of Buffer Circuits," IEEE J. Solid-State Circuits, SC-19, pp.468-473, 1984.

- [8] J.Mavor, M.Jack and P.Denyer, Introduction to MOS LSI Design, Addison-Wesley, 1083.

Fig.13 Short-circuit power of CMOS inverter per switching

Fig.12 Calculated and simulated delay with source/drain resistance

Fig.14 Transition voltage of CMOS inverter