# デプリーション形 CMOS ゲートの特性

## Characteristics of depletion type CMOS gate

°浅野 雄太郎

野瀬 浩一

桜井 貴康

Yutaro Asano

Ko-ichi Nose

Takavasu Sakurai

東京大学生産技術研究所

IIS, University of Tokyo

## 1. はじめに

スケーリング則による回路の高集積化に伴い、集 積回路の消費電力は急激に増大し続けており、大き な問題となっている。そのため、従来はスケーリン グされずに一定であった電源電圧が、近年では低消 費電力化をめざすために、5V から 3.3V、1.8V と急 速に下げられており、今後も低電源電圧化がトレン ドになると考えられている。しかしながら、電源電 圧を単独で低下させると、トランジスタの駆動能力 が低下してしまうため、回路の遅延時間が悪化する という問題が生じる。遅延時間を増加させないよう にするためには、電源電圧を下げるとともに、閾値 電圧も同時に低下させなければならない。回路に高 速性が求められるクリティカルパスなどでは、閾値 電圧が 0V 以下の depletion 形の CMOS 回路が使用 されるようになる可能性もある。そこで、本研究で は depletion 形 CMOS 回路の解析を行った。

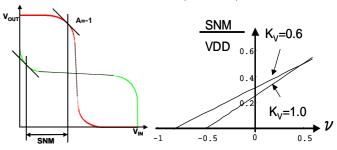

## 2. デプリーション形回路のノイズマージン

デプリーション形のインバータ回路では、エンハンスメント形に比べ電圧増幅率が低く、閾値をさらに低下させるとついには増幅率|A|<1となり、出力信号の振幅が入力信号の振幅よりも小さくなってしまう。従って、デプリーション形 CMOS には最低動作閾値電圧が存在する[1]。しかし、最低動作閾値電圧では、スタティックノイズマージン(SNM)が0であるため、実際にはある程度の余裕を考えなければならない。

MOS トランジスタのドレイン電流 Ids は、 乗則 [2]を用いて次のように表される。

$$V_{DSAT} = K_{V}(V_{GS} - V_{T})^{\alpha/2}$$

$$I_{DSAT} = K_{I}(V_{GS} - V_{T})^{\alpha} \qquad (V_{DS} \ge V_{DSAT})$$

$$I_{DSAT} = I_{DSAT}(2 - \frac{V_{DS}}{V_{DSAT}}) \frac{V_{DS}}{V_{DSAT}} \qquad (V_{DS} < V_{DSAT})$$

ここで、 は  $1 \sim 2$  の値をとる。Shockley モデルでは = 2 である。一般の について解析的に SNM を求めるのは困難であるが、 = 2 の時は、

SNM =

$$\frac{(1+2v)}{4}$$

( $K_V = 1.0$ ) ( $v = \frac{V_T}{V_{DD}}$ )

SNM =  $\frac{(5+6v)}{16}$  ( $K_V = 0.6$ )

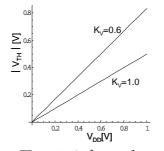

となる。従って、SNM は  $V_{GS}$ 、 $V_{DS}$  によらず、 および  $K_V$  のみに依存することがわかる。(閾値電圧 /

電源電圧)が SNM の大きさとトレードオフの関係になっていることがわかる。

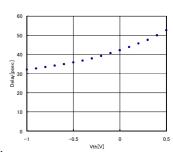

## 3. デプリーション形回路の遅延時間

回路モデルにより遅延時間を求める場合、エンハンスメント形ではプルアップパスまたはプルダウンパスの片方のみがオンであると多くの場合近似しているが、デプリーション形の場合は常に両方のパスに電流が流れている。そのため、NMOSによるインバータの放電を考える場合、PMOSから流れ込む電流との差分が実質的な放電電流になることを考慮する必要がある。

## 4. まとめ

デプリーション形 CMOS による、低電源電圧回路の遅延時間およびノイズマージンの考察を行った。

## 参考文献

[1] グェン・ドゥック・ミン、野瀬浩一、桜井貴康、" 低電源電圧 depletion 型 CMOS の最低動作閾値電 圧"、1999 年電子情報通信学会春季総合大会、A-3-12 [2] Takayasu Sakurai, R. Richard Newron, "A simple MOSFET for Circuit Analysis", IEEE Trans. on Electron Devices, Vol. 38, No. 4, 1991

図 1 SNM の定義

図 2 インバータにおける ノイズマージン

図 3 ノイズマージン一定 条件での V<sub>DD</sub>-V<sub>T</sub>特性

図 4 遅延時間の 閾値依存性