# LSIの新境地を切り開く 「スーパーコネクト」技術

東京大学、国際・産学共同研究センター 生産技術研究所 桜井貴康

E-mail:tsakurai@iis.u-tokyo.ac.jp

## LSIの新境地を切り開く「スーパーコネクト」技術

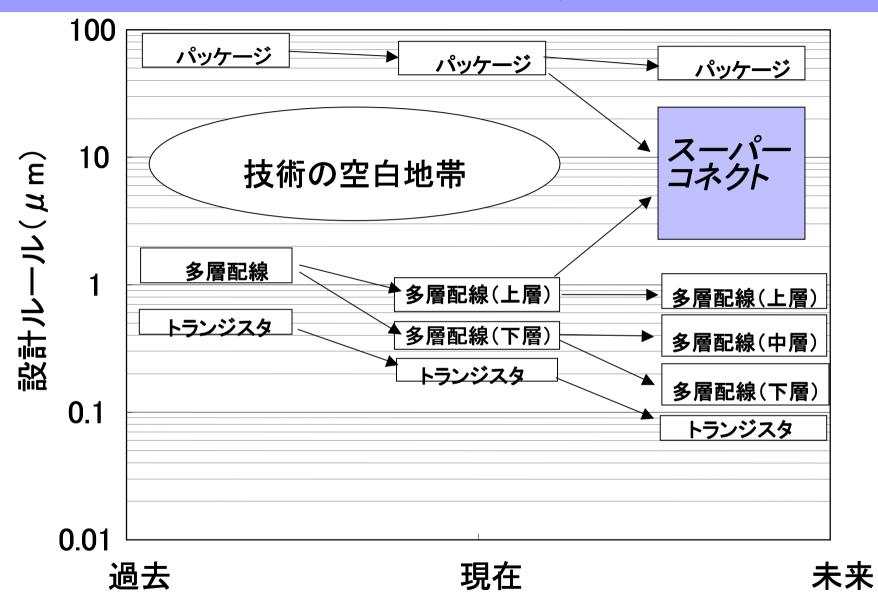

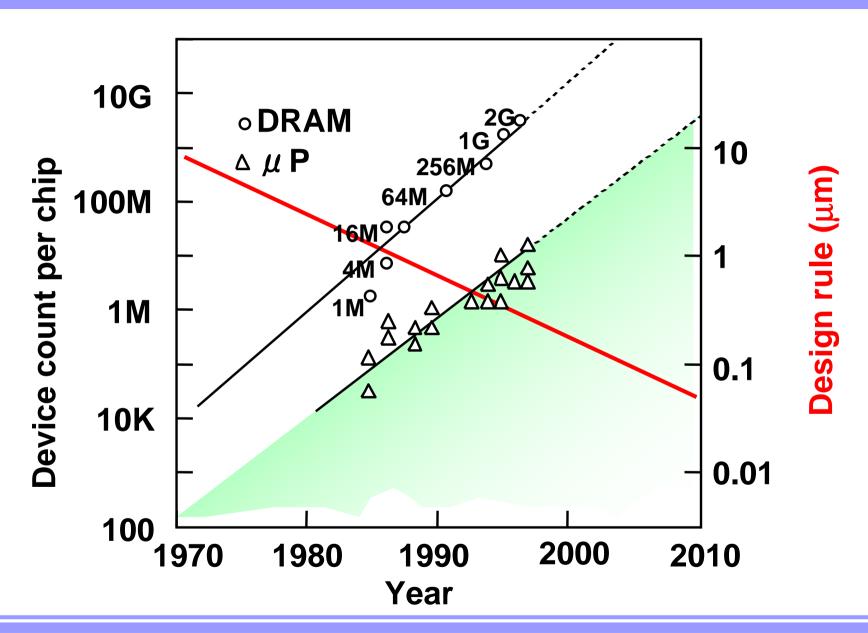

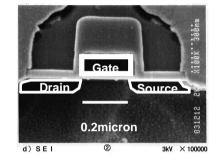

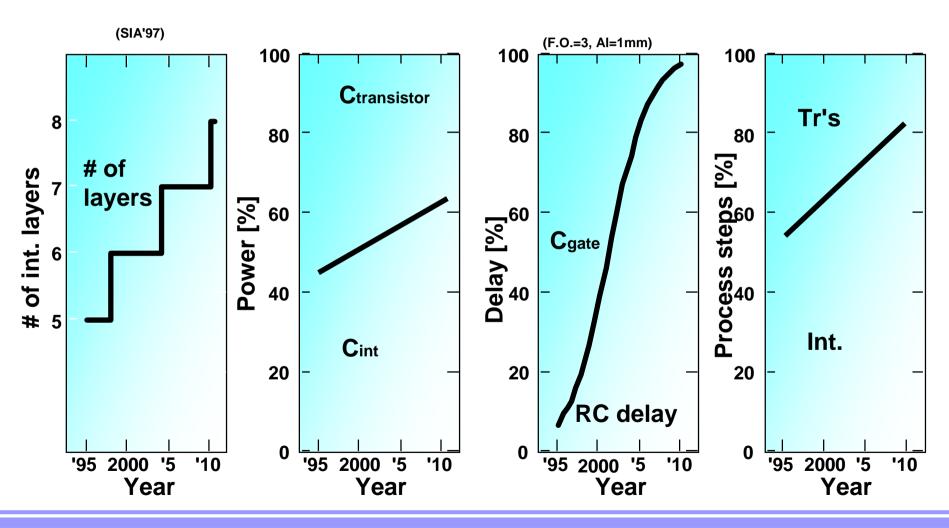

これから10年のLSIの技術的課題を展望すると、配線系に多くの問題が集中していることに気付く。 LSIの良し悪しを決める指標にはスピード、面積、消費電力、信頼性、ターンアラウンドタイムなどがある。従来はトランジスタがこれらの指標を決めてきた。しかし、ここにきて配線がこれらの指標を決めるというパラダイムシフトが起こっている。配線RC遅延の増大はLSIのスピードを律則し始めた。電源線の電流密度の増大は、信頼性の低下やIRドロップの増大といった問題を引き起こしている。配線の多層化によって製造期間は配線部で決まってくるようになった。

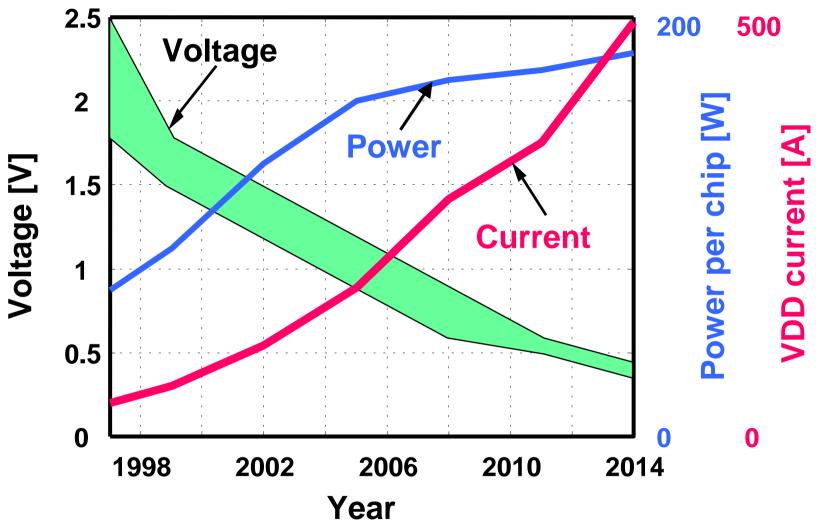

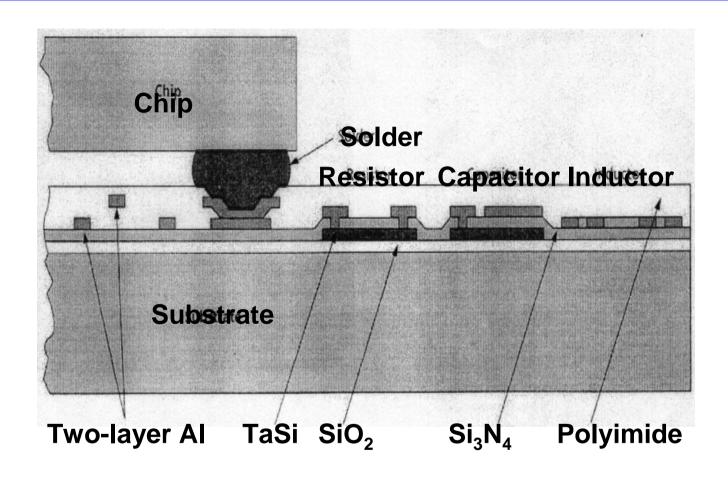

さて、このような問題を解決する上で従来のLSI上の配線だけでは限界が見えている。例えば電源線を考えてみよう。チップの消費電力は増大しており、電源電圧は低下している。International Technology Roadmap for Semiconductors によれば、2006年には160W、0.8Vといった電力と電源電圧値が出ている。すると、電源系は200Aの電流を運ぶ必要がある。チップの周辺にべったり電源パッドを配し、べた膜で配線できたとしても、中心部で5%の電圧降下しか許さないとすると0.5m  $\Omega$  以下のシート抵抗が必要となる。これには銅配線を仮定しても、数十  $\mu$  m以上の膜厚が必要になってくる。このような厚膜配線は従来のLSI技術ではむずかしい。この例は極端だとしても、1  $\mu$  m ~20  $\mu$  m程度の膜厚配線層が必要になるのは数年以内に起こると考えられる。

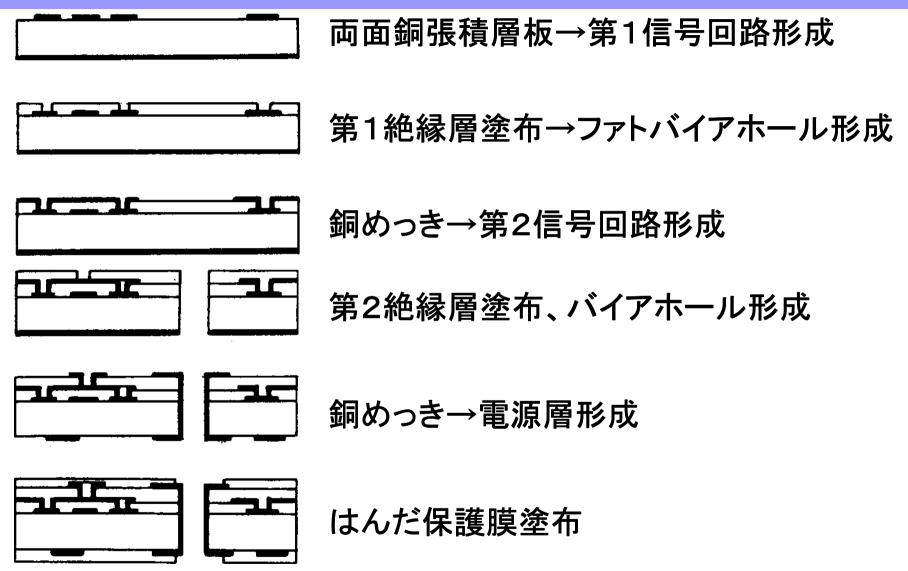

現在のところLSI上では1 $\mu$ m程度の配線膜厚が限度、一方プリント基板やパッケージなど実装側では数十 $\mu$ m以上というように、この中間部分の膜厚とデザインルールが欠落している。この辺の配線技術、すなわちスーパーコネクト技術が必要になってくる所以である。スーパーコネクトはLSI側と実装側双方の融合が図られる技術である。実装側もビルドアップ工法などLSIに近い製造法なども出てきて、LSIと実装との融合も取れやすい環境が整ってきている。マイクロパッドといった15 $\mu$ m角程度のパッド技術も実用化されている。

## LSIの新境地を切り開く「スーパーコネクト」技術(続)

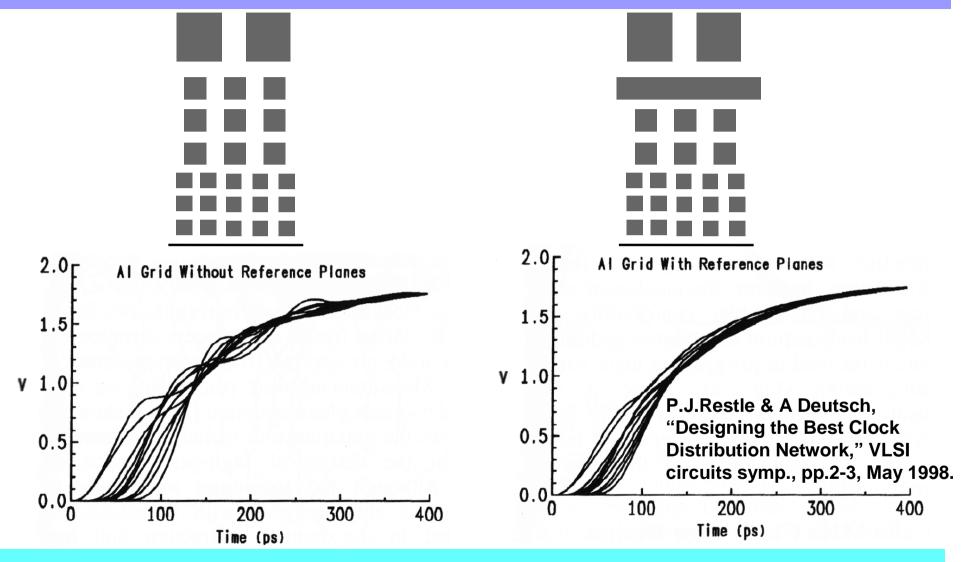

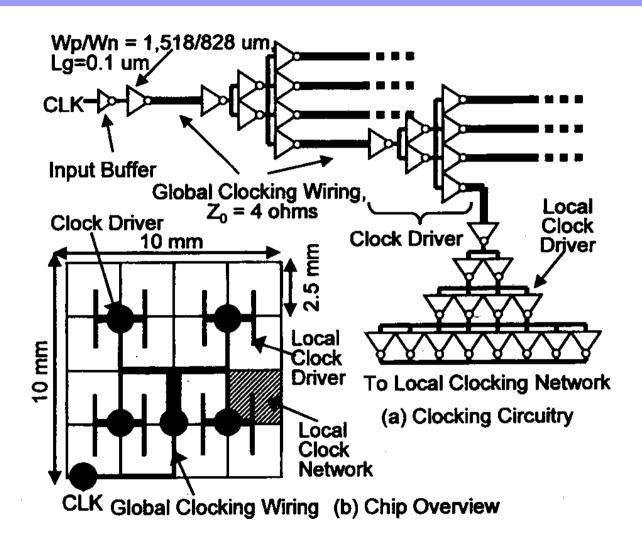

さて、このようなスーパーコネクトは配線遅延を軽減するにも役立つ。クロック系のスキューの低減は 頭のいたい課題だが、低抵抗な配線層があればスキューを小さくできる。従って、クロックの基幹系を スーパーコネクトで行いたい。それにはLSI上の配線とスーパーコネクトを同時にシームレスに設計 するコデザインが必要になってくる。

スーパーコネクトには、従来の配線問題の解決のみならず、新しい付加価値の創造という側面もある。 プロセスの異なるチップを高いバンド幅で繋ぐ技術は、システムをワンチップで構成するよりバランス のとれたソリューションを提供する。チップを積層するスーパーコネクトでは、チップを平面に並べるマ ルチ・チップ・モジュールより全体の配線距離を小さくできるので、システムがより小型、高性能になる。 熱の放散やインダクタンスの制御、特性インピーダンスの調整などにも利用できる可能性がある。 LSI上の配線とスーパーコネクトを並列して製造できればターンアラウンドタイムの減少にも寄与する。

少し振りかえってみると、配線技術がLSIのビジネスモデルを変えた例に気づく。配線の多層化によって、LSIの製造ターンアラウンドタイムが配線系によって決まるようになってきた。こうなると、ゲートアレイがセルベースのASICに対して持っている製造時間の優位性が保てなくなった。これを反映して、面積や性能的に有利なセルベースビジネスに主流が移行してきた。このように配線技術はビジネスモデルにも影響を与える。スーパーコネクトによってこれからのビジネスモデルが変わる可能性も十分にある。

## スーパーコネクト

#### **Cost of interconnect**

M.Pinto, "Atoms to Applets: Building Systems ICs in the 21st Century," ISSCC, pp.26-30, Feb. 2000.

# スーパーコネクト

| 目的     | 手段          | 具体策(LSI側)                | 具体策(実装側)    |

|--------|-------------|--------------------------|-------------|

| 高速化    | 配線長の短縮      | 多層化   逆スケーリング            | 3次元積層       |

|        | RC遅延の削減     | Cu + Iow-k               | low-k       |

|        | ──L遅延の考慮    | 今後インダクタンス考慮              | 既にインダクタンス考慮 |

|        | リピータ        | リピータ内蔵配線                 | 3次元積層       |

|        | ──[IRドロップ   | 厚膜配線、幅広配線                | 厚膜配線、幅広配線   |

|        | ゲート遅延の削減 ー  | トランジスタの微細化               |             |

|        |             |                          |             |

| 低消費電力化 | 配線部の電力削減    | Cu + Iow-k               |             |

|        | ──配線長の短縮    | 多層化                      | 3次元積層       |

|        | トランジスタの低電力化 | 微細化,SOI,・・・              |             |

|        |             |                          |             |

|        |             | スーパーコネクト<br>LSI側と実装側が共通の | り技術へ        |

|        |             | 従来の枠組みが変わる               |             |

出典:日経マイクロデバイス

# スーパーコネクト

| 目的    | 手段                                                               | 具体策(LSI側)                                         | 具体策 ( 実装側 )                              |

|-------|------------------------------------------------------------------|---------------------------------------------------|------------------------------------------|

| 高信頼性化 | <ul><li>─ マイグレーション対策</li><li>─ 放熱対策</li><li>─ 接続信頼性の向上</li></ul> | Cu , Cu + Mg サーマル・ビア                              | サーマル・ビア 各種バンプ/バンプレス接合                    |

| 小型化   | ─ <u>「チップの小型化</u><br>─ <mark>パッケージの小型化</mark>                    | 微細化                                               | チップ・サイズ実装<br>3次元積層<br>マイクロパッド            |

| 多機能化  |                                                                  | 高集積化 , システムLSI  ③次元LSI  オン・チップ・インダクタ  オン・チップ・アンテナ | 微小MCM<br>3次元積層<br>RLC内蔵プリント基板<br>超小型アンテナ |

|       |                                                                  | スーパーコネクト<br>LSI側と実装側が共通の<br>従来の枠組みが変わる            |                                          |

出典:日経マイクロデバイス

## **Moore's Law**

## **Scaling Law**

| Tran                           | sistor                     | N     | umbers are   | exponent t | o k (k <sup>n</sup> ) |

|--------------------------------|----------------------------|-------|--------------|------------|-----------------------|

| Voltage                        | [V]                        |       | -1           |            |                       |

| Tr. size                       | [x]                        |       | -1           |            |                       |

| Oxide thickness                | [t]                        |       | -1           |            |                       |

| Current                        | [I~V <sup>1.3</sup> /t]    |       | - 0.         | .3         |                       |

| Tr. capacitance                | [Cg~x <sup>2</sup> /t]     |       | -1           |            |                       |

| Tr. delay                      | [Tg~CgV/I]                 |       | -1.7         | 7          |                       |

| Tr. power                      | [Pg~CgV <sup>2</sup> /Tg]  |       | <u>-1.</u> ; | 3          |                       |

| Tr. power dens                 | ity [p~Pg/x <sup>2</sup> ] |       | 0.           | 7          |                       |

| Tr. desity                     | [n~ 1/x²]                  |       | 2            | 2          |                       |

| Interconn                      | ection                     | Local | Middle       | Global     | VDD/VSS               |

| Length                         | [L]                        | -1    | - 0.5        | 0          | 0                     |

| Width                          | [W]                        | -1    | - 0.5        | 0          | 1                     |

| Thickness                      | [T]                        | -1    | - 0.5        | 0          | 1                     |

| Height                         | [H]                        | -1    | - 0.5        | 0          | 0                     |

| Resistance                     | [Rm~L/W/T]                 | 1     | 0.5          | 0          | -1                    |

| Capacitance                    | [Cm~LW/H]                  | -1    | - 0.5        | 0          | 1                     |

| RC Delay/Tr. delay[Tm~RmCm/Tg] |                            | 1.7   | 1.7          | 1.7        | -                     |

| Current density [J~pLW/V/W/T]  |                            | _     | -            | -          | 0.7                   |

| Dc Noise [                     | SNdc~JWLR <sub>m</sub> /V] | _     | _            | -          | 1.7                   |

$$hs = \frac{\mu \varepsilon}{tox} \left( \frac{W}{L} \right) \frac{(V gs - V t)}{2} \sim [V \alpha / t]$$

$$\alpha = 1.3$$

T.Sakurai&A.Newton,"Alpha-power law MOSFET model and its application to CMOS inverter delay and other formulas",IEEE JSSC, vol25, no,2, pp.584-594, Apr. 1990.

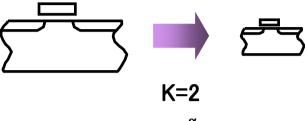

## **Scaling Law**

**Size 1/2**

#### **Favorable effects**

| Size           | x1/2      |

|----------------|-----------|

| Voltage        | x1/2      |

| Electric Field | <b>x1</b> |

| Speed          | <b>x3</b> |

| Cost           | x1/4      |

#### **Unfavorable effects**

| Power density      | x1.6      |

|--------------------|-----------|

| RC delay/Tr. delay | x3.2      |

| Current density    | x1.6      |

| Voltage noise      | x3.2      |

| Design complexity  | <b>x4</b> |

## Three crises in VLSI designs

- Power crisis

- Interconnection crisis

- Complexity crisis

## Interconnect determines cost & perf.

P: Power, D: Delay, A: Area, T:Turn-around

## VDD, Power and Current Trend

International Technology Roadmap for Semiconductors 1998 update sponsored by the Semiconductor Industry Association in cooperation with European Electronic Component Association (EECA), Electronic Industries Association of Japan (EIAJ), Korea Semiconductor Industry Association (KSIA), and Taiwan Semiconductor Industry Association (TSIA)

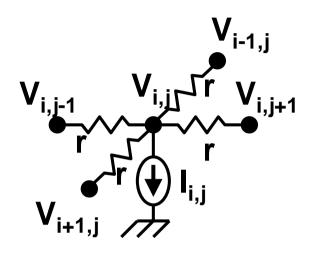

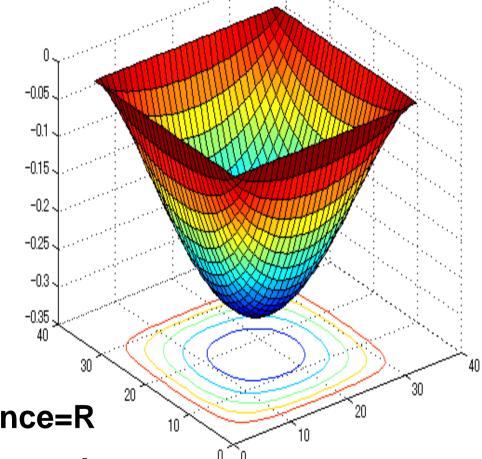

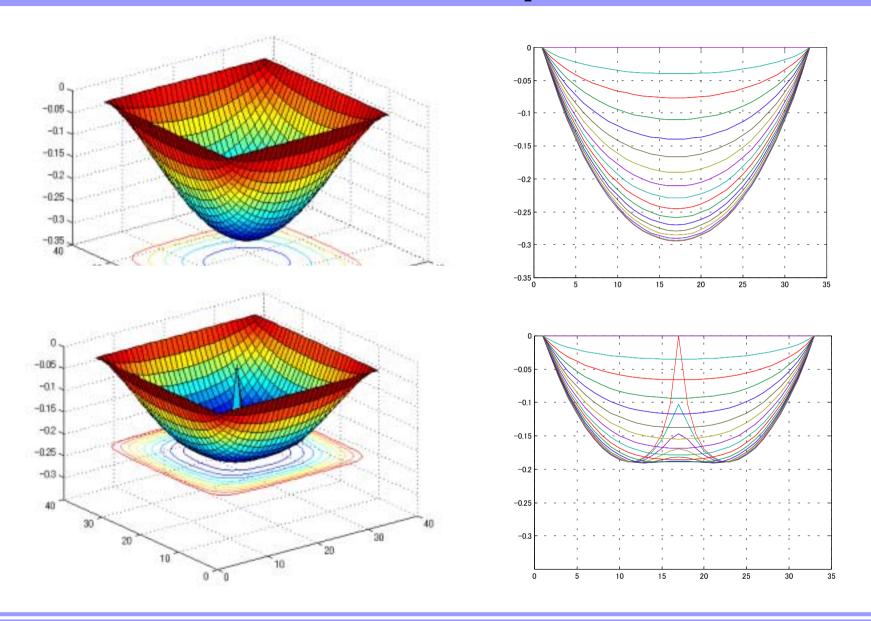

## **IR Drop**

$$V_{i,j} = (V_{i-1,j} + V_{i+1,j} + V_{i,j-1} + V_{i,j+1})/4 - r I_{i,j}$$

$\Sigma$ I<sub>i,j</sub>=I, Sheet resistance=R

Take IR as unity voltage drop

## **IR Drop**

T.Sakurai

#### Interconnect Cross-Section and Noise

**Unscaled / anti-scaled**

- Clock

- Long bus

- Power supply

• Signal

1V 20W -> 20A current

2% noise on VDD & VSS -> ~0.02V / 20A -> ~10µm thick Cu Thick layer on LSI, area pad, package are co-designed.

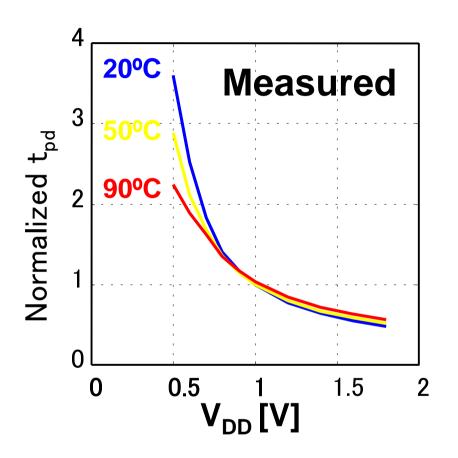

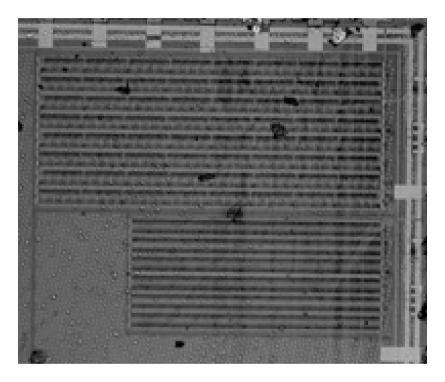

#### Measurement of 32bit full adder

Photograph of 32bit FA 0.3μm CMOS

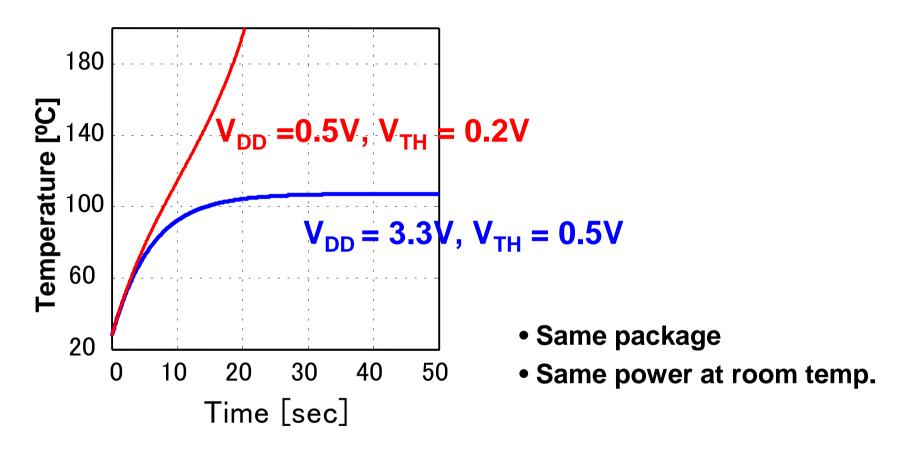

#### Transient response of chip temperature

# Better package is needed to avoid thermal runaway in low voltage.

K.Kanda, K.Nose, H.Kawaguchi, and T.Sakurai, "Design Impact of Positive Temperature Dependence of Drain Current in Sub 1V CMOS VLSI's ", CICC99, pp.563-566, May 1999.

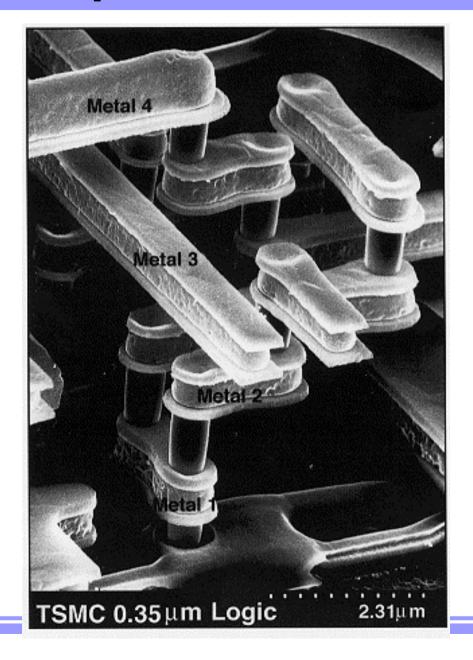

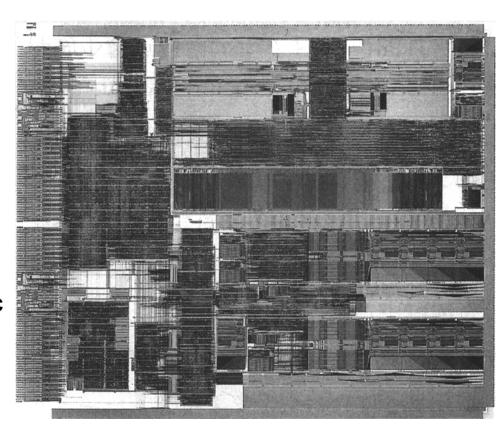

## **Complex interconnect**

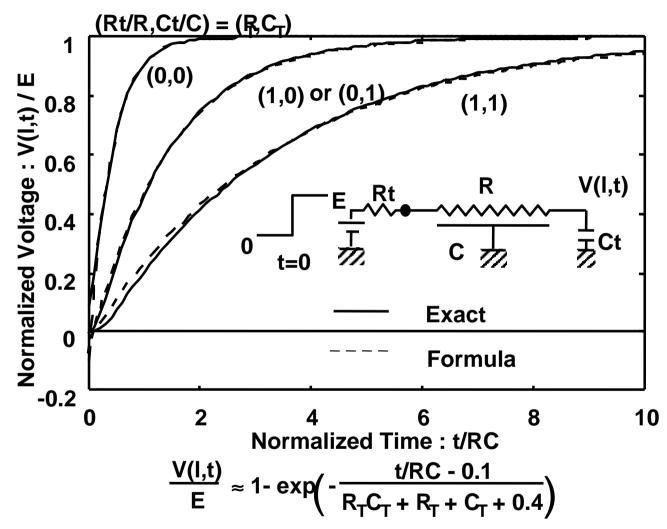

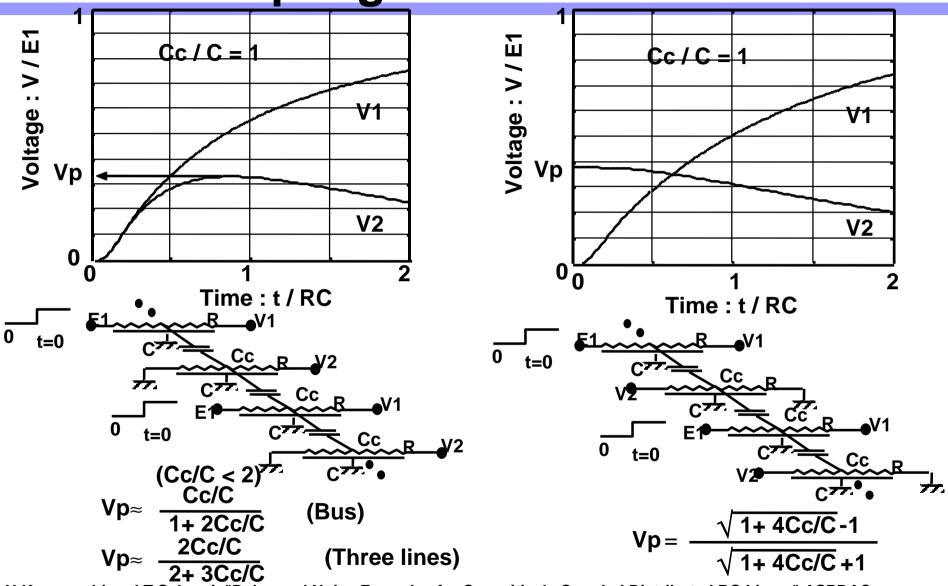

#### Voltage waveforms of a distributed RC line

T.Sakurai, "Closed-Form Expressions for Interconnection Delay, Coupling and Crosstalk in VLSI's," IEEE Trans. on ED, Vol.40, No.1, pp.118-124, Jan.1993.

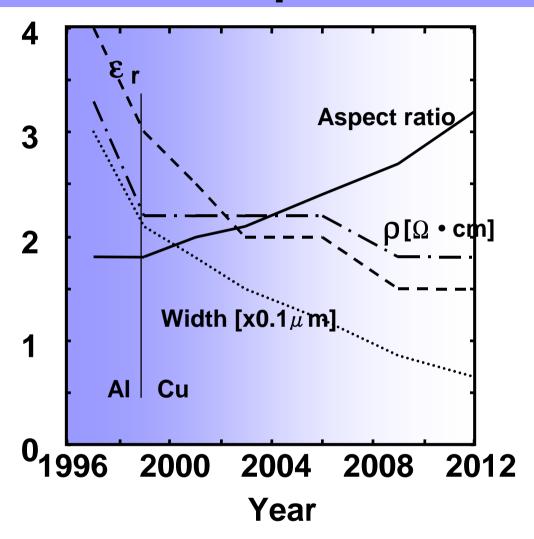

## Interconnect parameters trend

Semiconductor Industry Association roadmap http://notes.sematech.org/1997pub.htm

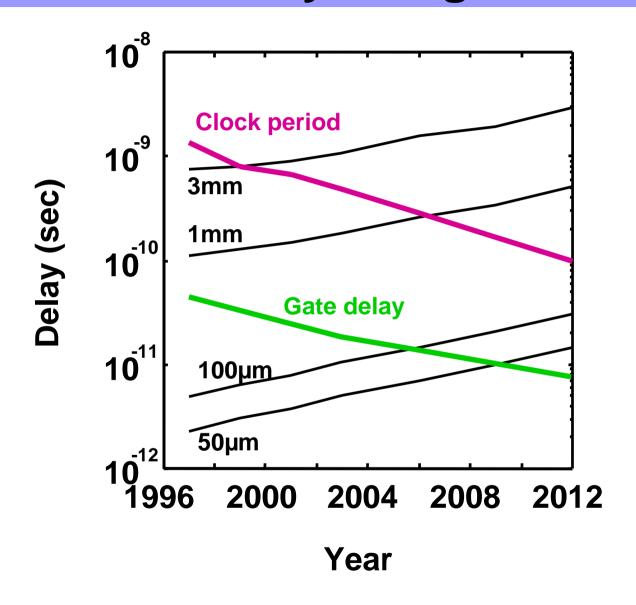

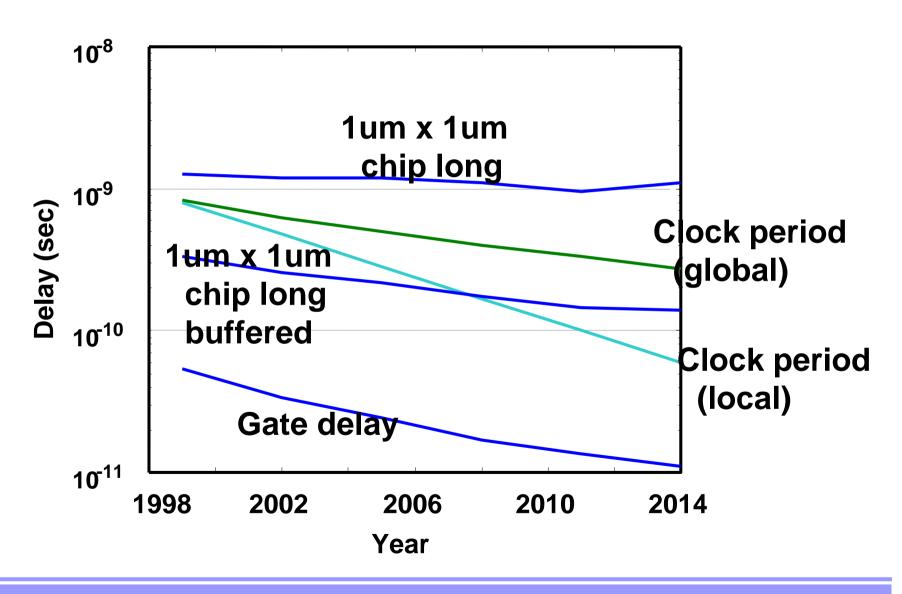

## RC delay and gate delay

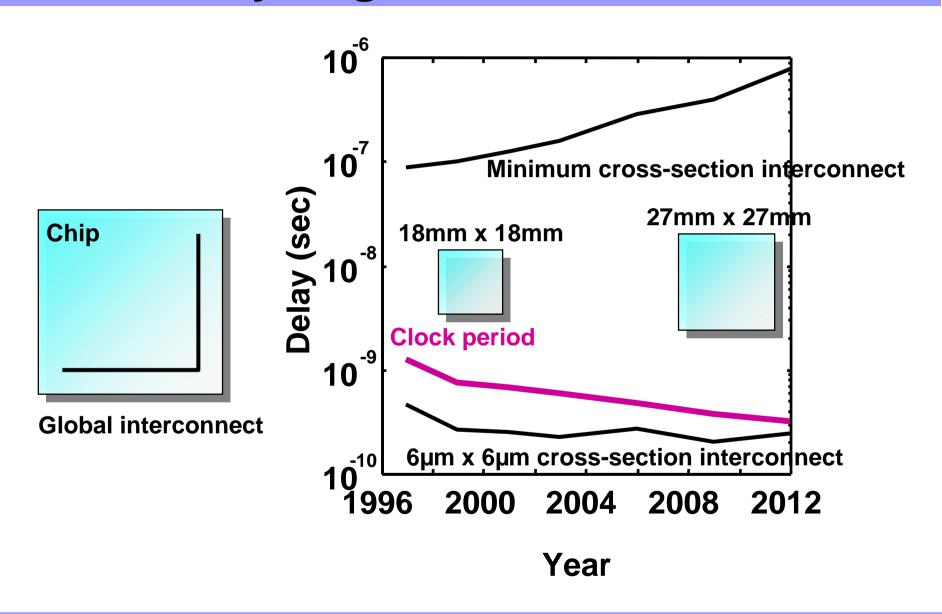

## RC delay of global interconnections

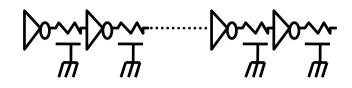

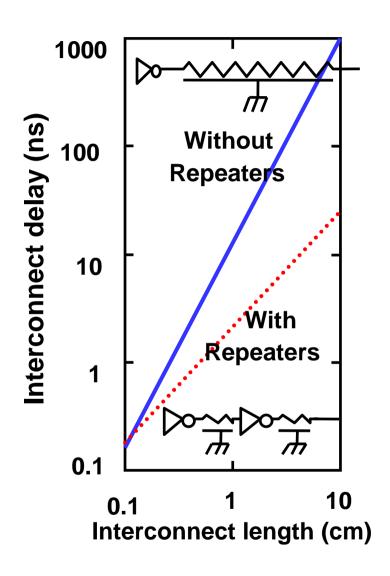

## Repeaters

$$C_T$$

$R_T$

$C_{INT}$

a) Without repeaters

b) With repeaters

$$t_{05} \approx 0.377 R_{INT} C_{INT} + 0.693 (R_T C_T + R_T C_{INT} + R_{INT} C_T)$$

C<sub>0</sub>: Gate capacitance of minimum MOSFET

R<sub>o</sub>: Gate effective resistance of minimum MOSFET

Delay

$$\approx k \left[ p_1 \frac{R_{INT}}{k} \frac{C_{INT}}{k} + p_2 \left( \frac{R_0}{h} hC_0 + \frac{R_0}{h} \frac{C_{INT}}{k} + \frac{R_{INT}}{k} hC_0 \right) \right]$$

: Buffered

$$\frac{\partial Delay}{\partial h} = \mathbf{0} \rightarrow h_{OPT} = \sqrt{\frac{C_{INT}R_0}{R_{INT}C_0}}: Optimized size of buffer inverter$$

$$\frac{\partial Delay}{\partial k} = \mathbf{0} \rightarrow k_{OPT} = \sqrt{\frac{p_1}{p_2}} \sqrt{\frac{R_{INT}C_{INT}}{R_0C_0}} : Optimized number of stages$$

$$Delay_{OPT} = 2\left(\sqrt{\rho_1\rho_2} + \rho_2\right)\sqrt{R_{INT}C_{INT}R_0C_0} \approx 2.4\sqrt{\tau_{INT}\tau_{MOS}}$$

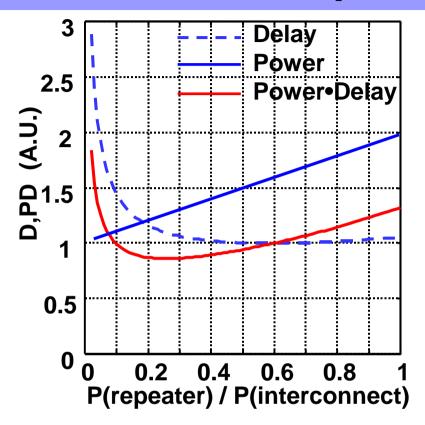

#### **Delay and Power Optimization for Repeaters**

#### **Delay optimized**

→P: P(repeater)=0.60 P(interconnect)

#### Power Delay optimized

**→D:** 1.09 Dopt

→P: P(repeater)=0.26 P(interconnect)

→PD: 0.86 of Dopt case

## **Buffered interconnect delay**

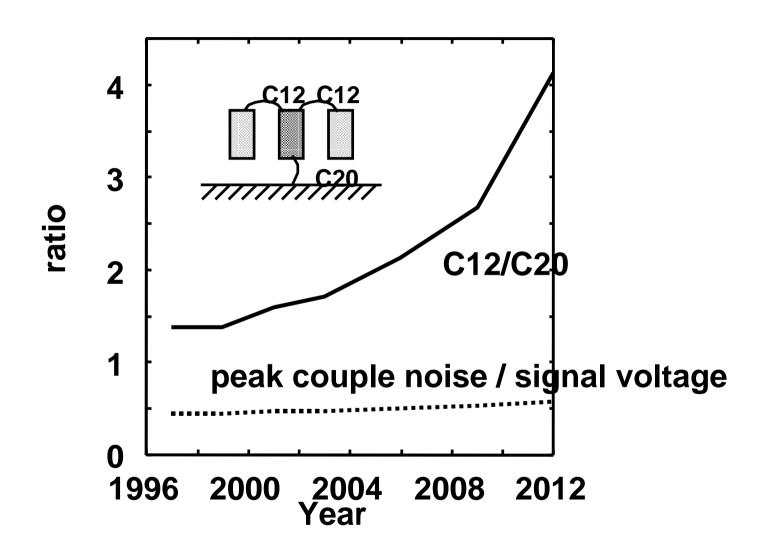

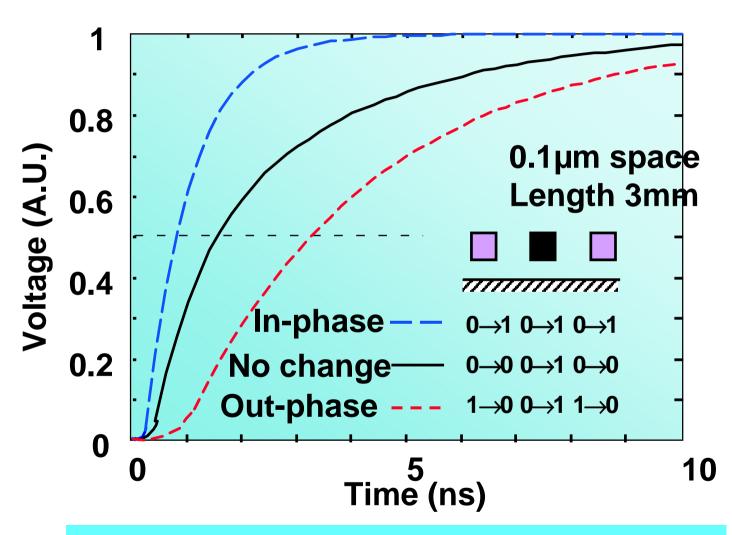

## **Capacitive Coupling Noise**

## Coupling noise in RC bus

H.Kawaguchi and T.Sakurai, "Delay and Noise Formulas for Capacitively Coupled Distributed RC Lines," ASPDAC, Digest of Tech. Papers, pp.35-43, Feb. 1998.

## **Coupling among Interconnection**

Difficulty in checking setup and hold time.

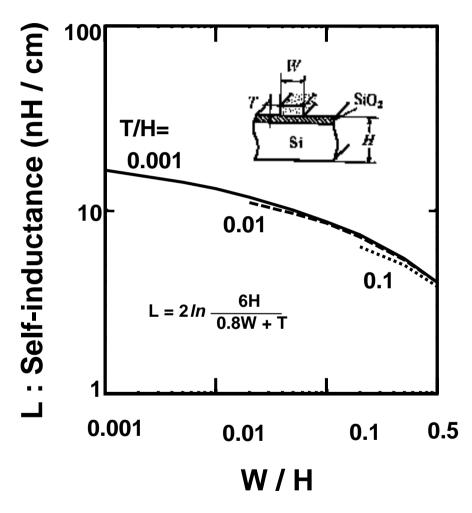

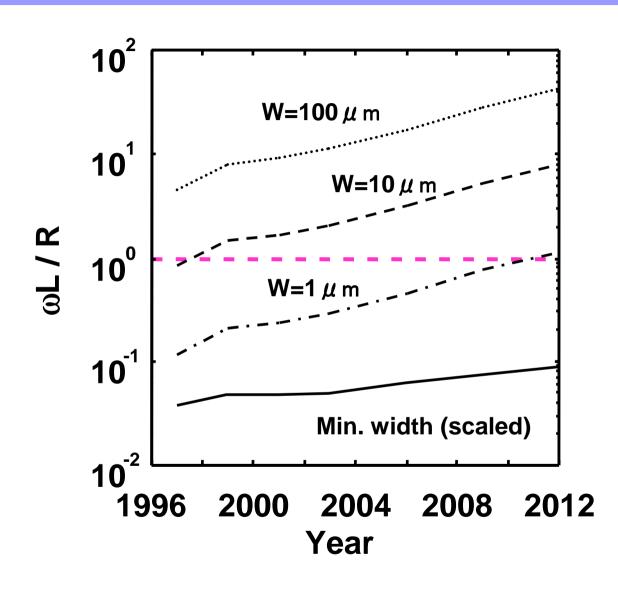

#### Inductance?

- Now RC effects surmounts LC effects because R > |jωL|.

- In the future, both of R and ωL increase (R increases more rapid?).

- Exception in low-R lines

- Inductive effects in wide clock lines in a fast processor are claimed to be observed in simulation.

- Clock lines are placed on power plane to reduce inductive effects.

- [1] D.A.Priore, "Inductance on Silicon for Sub-micron CMOS VLSI,"

Symp. on VLSI Circuits, 1993.

## **Inductive Effects**

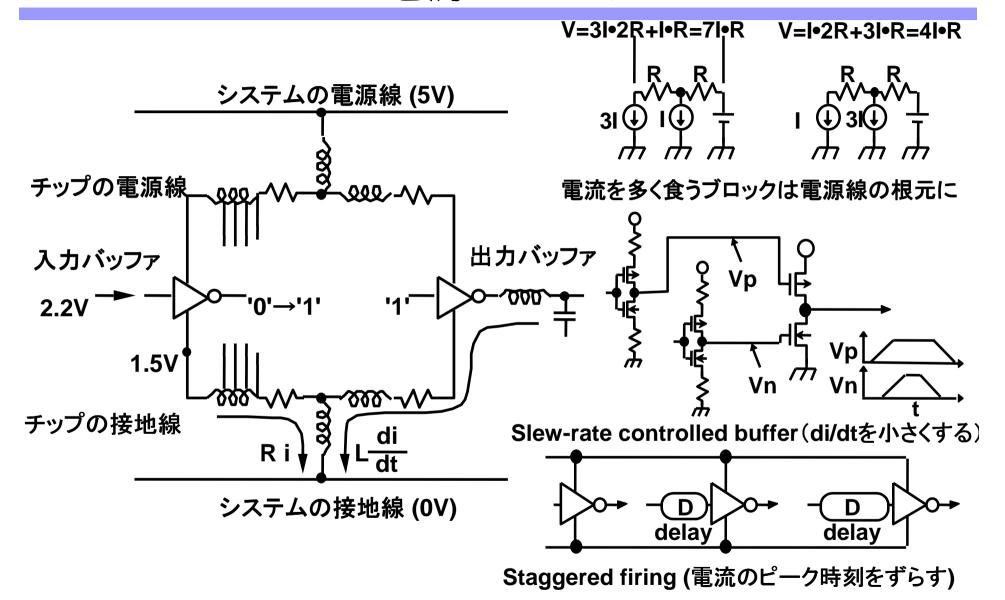

## 電源ノイズ

T.Sakurai

#### **Inductive Effects in Clock Lines**

Board design practice is imported in LSI.

#### H-tree clock distribution

M.Mizuno, K.Anjo, Y.Sumi, H.Wakabayashi, T.Mogami, T.Horiuchi, M.Yamashina, "On-Chip Multi-GHz Clocking with Transmission Lines," ISSCC, pp.366-367, Feb. 2000

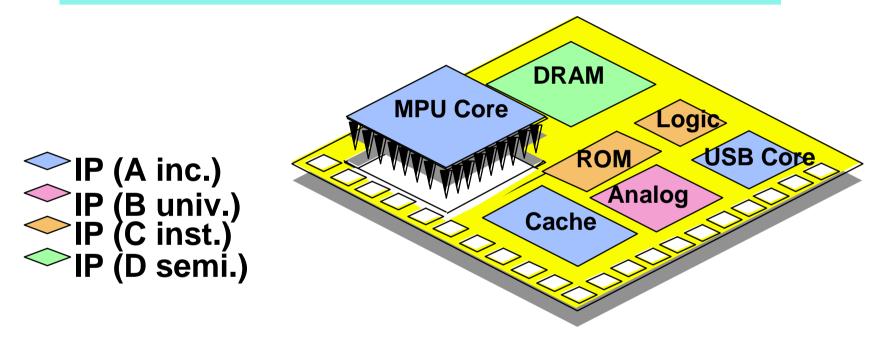

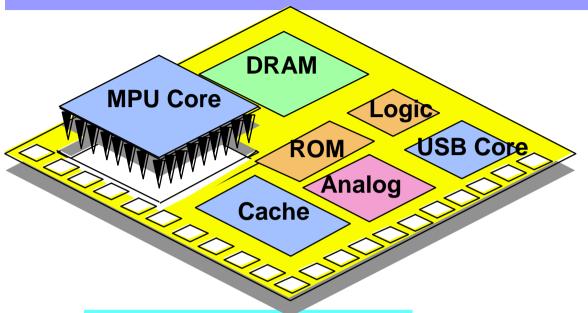

## System on a Chip (SoC)

- Re-use and sharing of design

- Design in higher abstraction

IP; CPU, DSP, memories, analog, I/O, logic...

HW/FW/SW

## **System LSI for Games**

- Clock freq. 300MHz

- 10M transistors

- Graphics synthesizer integrate40M tr. With embedded DRAM

- Memory bandwidth 3.2GB/s

- Floating operation 6.2GFLOPS/sec

- 3D CG 6.6M polygon/sec

- MPEG2 decode

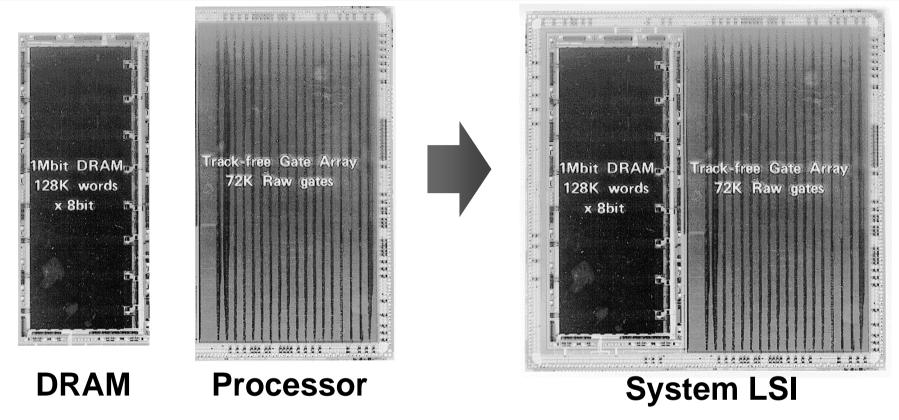

# DRAM embedding

K.Sawada, T.Sakurai, et al, "A 72K CMOS Channelless Gate Array with Embedded 1Mbit Dynamic RAM," in Proc. CICC'88, pp.20.3.1-20.3.4, May 1988.

Two orders of magnitude improvement in bandwidth and power

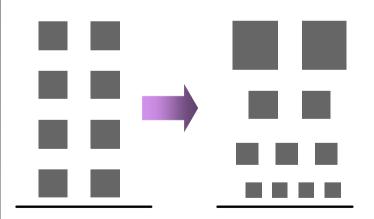

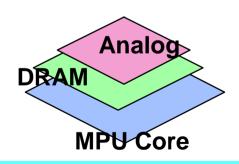

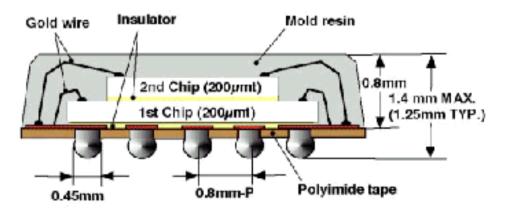

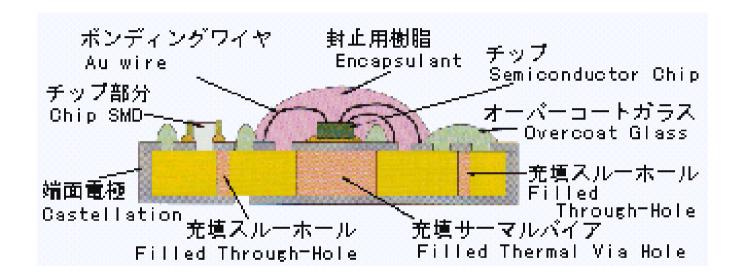

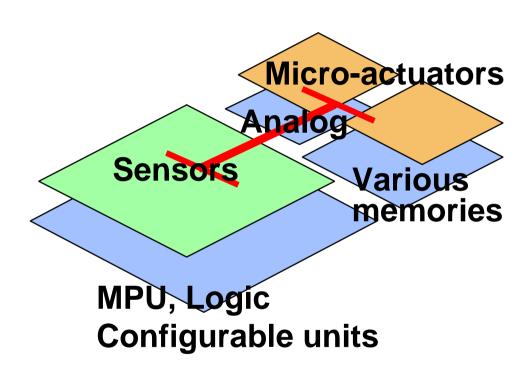

# Stacked chips

- Smaller area

- Shorter interconnect

- Optimized process for each die (Analog, DRAM, MEMS…)

- Good electrical isolation

- Heat dissipation is an issue

#### System on a chip

Stacked chips

藤田他、「スタックドCSP技術」、シャープ技法、1998.8

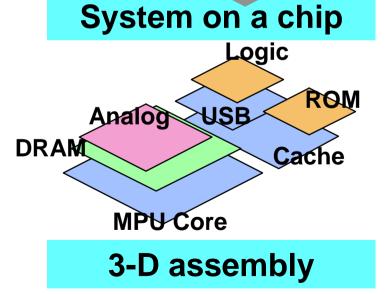

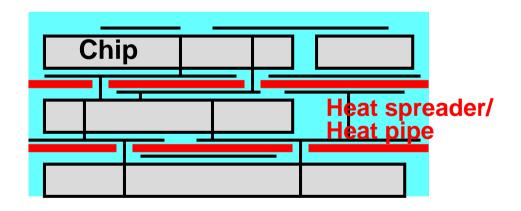

# 3-Dimensional assembly

- Smaller area

- Shorter interconnect

- Optimized process for each die (Analog, DRAM, MEMS...)

- Good electrical isolation

- Through-chip via

- Heat dissipation is an issue

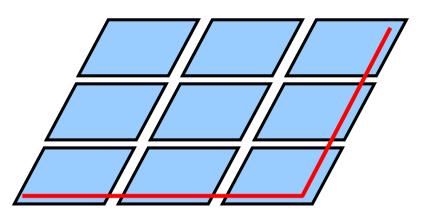

# Shorter interconnect in 3-D assembly

System on a chip

3-D assembly

$$\frac{\# of \ devices \ in \ d \ (3D)}{\# of \ devices \ in \ d \ (2D)} = \frac{1}{3} \left( 2\frac{d}{h} + \frac{h}{d} \right)$$

$$\approx \frac{2}{3} (\# of stacked chips in d)$$

d: Manhattan distance

h: Height between chips

# System-in-Package (SIP)

K.L.Tai, "System-In-Package (SIP): Challenges and Opportunities," ASPDAC, pp.191-196, Jan. 2000

# ビルドアップ基板

日本ビクター, 10層のビルドアップMCM基板を展示, ライン/スペースは30  $\mu$  m/30  $\mu$  m http://ne.nikkeibp.co.jp/NE/1998/eleshow98/42556.htm

### Thermal via

ミヨシ電子工業: http://www.elec.co.jp/1\_kaisya/Page1410.html

# System-in-Package

Expanding role of packaging seen relegating SoC to niche status

# System-chip may topple

By Robert Ristelhueber

INDIAN WELLS, CALIF. - The wheels might be coming off the systemon-chip (SoC) bandwagon, if the chatter at last week's Dataquest Semiconductor conference is any barometer of industry sentiment. Heavyweights including IBM and Lucent Technologies indicated that costs may relegate SoC to niche status, with new packaging techniques stepping into the breach.

"A couple of years ago we really thought that the embedded DRAM model would be the panacea for many applications," said John Kelly, general manager of IBM Microelectronics. "It's not always the right thing. In many applications it still remains much cheaper to do it with multichip modules. It gives you satisfactory performance and often for lower cost."

"We have systems-on-chip now that are really 'system on chips,' " said John Dickson. president of Lucent Technologies' Microelectronics Group. "We do it that way because it's

most cost-effective, and the customer will prefer it that way because it offers more flexibility."

The subject was broached at the conference here by a Dataquest analyst who claimed that SoC designs will increasingly be supplanted in coming years by multichip packaging as higher mask costs squeeze SoC profitability.

Chip designers have often been willing to add mask steps ► CONTINUED ON PAGE 6

IBM's Kelly: 'In many apps, cheaper to do it with multichip modules."

# ... as industry grapple with impact of cores mode

By Peter Clarke and Brian Fuller

EDINBURGH, SCOTLAND - Intellectual property cores were a hot topic last week, both here at the IP99 Europe conference and at Dataquest Inc.'s annual semiconductor conference in Indian Wells, Calif. But as the industry struggles with new business

tomer-supplier re adding mask levels." lationships

ment on either side of the At ing chip-scale packaging, Fuhs lantic on how the cores marke said. "This enables you to build will unfold.

ment: IP cores and design reus standard logic can be done in

In some apps, multichip modules do the job more cheaply, conference told

#### 'System-in-package' could make SoC a niche

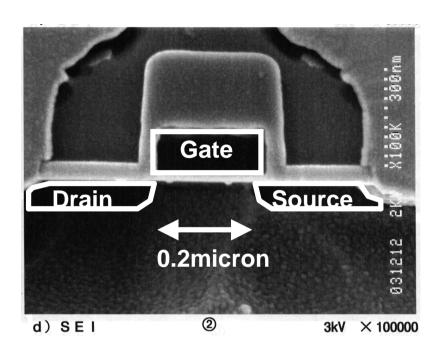

►CONTINUED FROM PAGE I and complexity to their logic devices in order to place analog and memory functions onto chips. "But when we get below 0.2 micron we get a cost shock, and the [return on investment] \sqrt{ will be diminished or even eliminated in many cases," said Clark Fuhs, vice president and director of Dataquest's Semiconductor Manufacturing Programs.

Mask costs will dramatically rise at deep submicron because of the use of phase-shift and optical proximity correction techniques as well as more expensive, 193-nm lithography equipment, putting low-volume SoC at a cost disadvantage, Fuhs said.

Militating against SoC designs for many applications is the wide disparity in revenue per square inch among the various blocks in the chip. Fuhs said. "The DSP or microprocessor block can be getting \$150 or \$200 per square inch, the FPGA about \$120, the analog block about \$35, the memory block about \$50 to \$60 . . . You're basically diluting your high-value logic pieces with all these other low-value pieces, yet you're models, new cus adding cost because you're

an An alternative is to fabricate fast-moving tech the different blocks as discrete nology, there was scant agree chips, placed close together usthe pieces in fabs that are optimized for those pieces. You can \( \square\) "Mask sets cost in excess of a On one thing there was agree build analog in a 0.7-micron fab,

0.35 or even 0.5 micron, and for the memory you can buy a wafer from somebody and break it up. The package is more expensive, but the overall system cost is going to be substantially less.

"The concept here is to take some level of interconnect . . . and simply move [it] from the chip into the package."

Fuhs noted that Intel's Pentium III is actually an 11-level-

metal device-six levels of aluminum inside the chip and five levels of copper outside. And he showed a photograph of a Sony digital Handycam, which he said contains 20 chip-scale devices, "so this technology is here,

it's real." In the not-toodistant future, he said, wafer foundries will give customers a choice of implementing a design either as a system-on-chip or as several discrete devices using chip-scale packaging.

To survive, the SoC must evolve to fit a more standardproduct model that would allow it to increase volume and become more cost-efficient, Fuhs said. He predicted that within five years, multichip packaging will be growing faster than SoC designs.

That view has its detractors. couple hundred thousand dollars, whether you do small chips or large chips," said National Semiconductor Corp... chief executive officer Brian . Halla, who has championed the notion of an information appliance-on-a-chip. "I can get tremendously more performance out of the same square inches of silicon by having it all together instead of having it two inches apart on a board.

"SoC isn't a marketing cru-

sor, because the pace of innovation differs between those parts; but Intel's upcoming Timna processor, he said, combines both functions.

"Having said all that, there are cases where we agree [about putting a system on a package]," he said. "There is a substrategy of ours called integrated disintegration, which means... there are analog functions you can pull off the chip because they are such a tiny portion of the overall chip, and yet they are the most difficult thing to port to the next-generation [process] technology."

IBM's Kelly said that "SoC integration has to be done se-

National's Halla touts 'integrated disintegration."

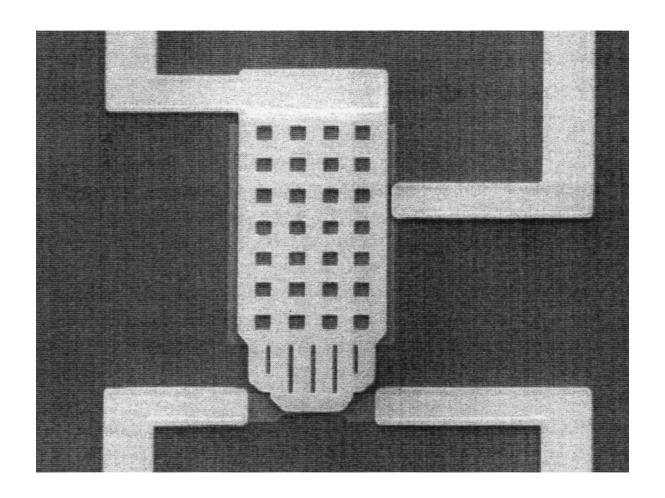

# Micro-machined mechanical switch

G.Weinberger, "The New Millennium: Wireless Technologies for a Truly Mobile Society," ISSCC, pp.20-24, Feb. 2000.

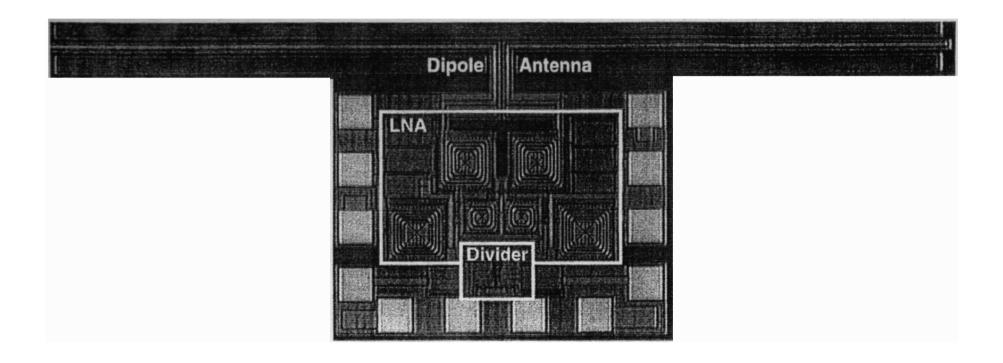

# Antenna on chip

B.Floyd, K.Kim and Kenneth, "Wireless Interconnection in a CMOS IC with Integrated Antennas," ISSCC, pp.328-329, Feb. 2000.

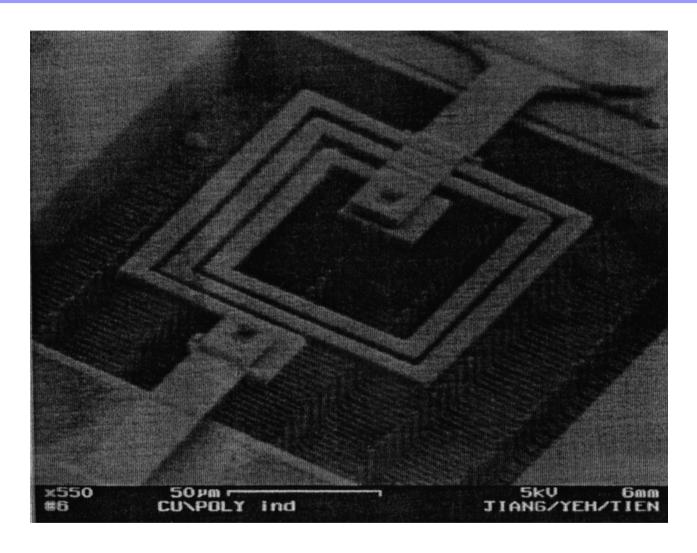

# Suspended spiral inductor

H.Jiang J.Yeh, Y.Wang, N.Tien, "Electromagneticallt Shielded High-Q CMOS-Compatible Copper Inductor," ISSCC, pp.330-331, Feb. 2000.

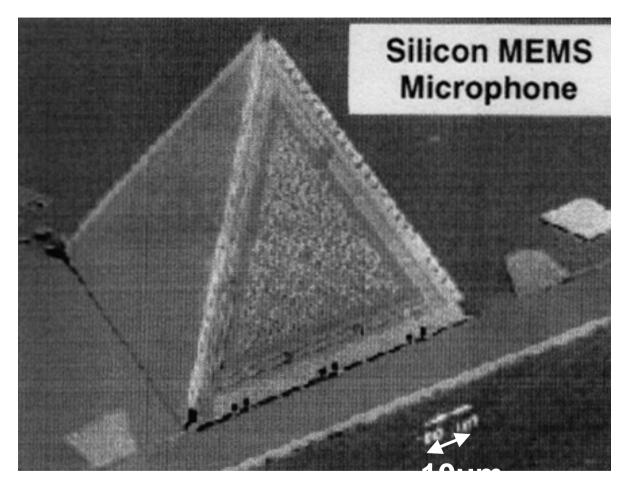

# Silicon MEMS microphone

Will soon exceed the performance of the best commercial microphones, yet be inexpensive and potentially integrated with on-chip electronics.

M.Pinto, "Atoms to Applets: Building Systems ICs in the 21st Century," ISSCC, pp.26-30, Feb. 2000.

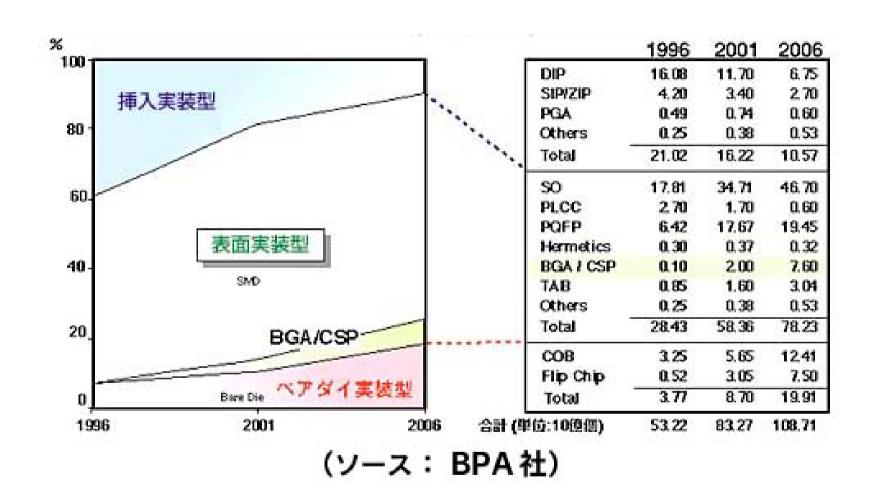

# ICパッケージの世界市場動向

http://www.ic.nec.co.jp/pkg/japanese/jissou/1/1\_1/1\_1\_2/

### **LSI in 2014**

| Year                    | Unit      | 1999 | 2014  | Factor |

|-------------------------|-----------|------|-------|--------|

| Design rule             | μm        | 0.18 | 0.035 | 0.2    |

| Tr. Density             | /cm2      | 6.2M | 390M  | 30     |

| Chip size               | mm2       | 340  | 900   | 2.6    |

| Tr. Count per chip (µP) |           | 21M  | 3.6G  | 170    |

| DRAM capacity           |           | 1G   | 1T    | 256    |

| Local clock on a chip   | Hz        | 1.2G | 17G   | 14     |

| Global clock on a chip  | Hz        | 1.2G | 3.7G  | 3.1    |

| Power                   | W         | 90   | 183   | 2.0    |

| Supply voltage          | V         | 1.5  | 0.37  | 0.2    |

| Current                 | Α         | 60   | 494.6 | 8      |

| Interconnection levels  |           | 6    | 10    | 1.7    |

| Mask count              |           | 22   | 28    | 1.3    |

| Cost / tr. (packaged)   | µcents    | 1735 | 22    | 0.01   |

| Chip to board clock     | Hz        | 500M | 1.5G  | 3.0    |

| # of package pins       |           | 810  | 2700  | 3.3    |

| Package cost            | cents/pin | 1.61 | 0.75  | 0.5    |

International Technology Roadmap for Semiconductors 1998 update sponsored by the Semiconductor Industry Association in cooperation with European Electronic Component Association (EECA), Electronic Industries Association of Japan (EIAJ), Korea Semiconductor Industry Association (KSIA), and Taiwan Semiconductor Industry Association (TSIA), International Technology Roadmap for Semiconductors: 1999 edition. Austin, TX:International SEMATECH, 1999.

# Possible electronic system in 2014

- Sensors/actutors

- 0.035µm 3.6G Si FET's with VTH & VDD control

- Locally synchronous 17GHz clock, globally asynchronous

- Chip / Package / Board system co-design for power lines, clocks, and long wires (superconnect)

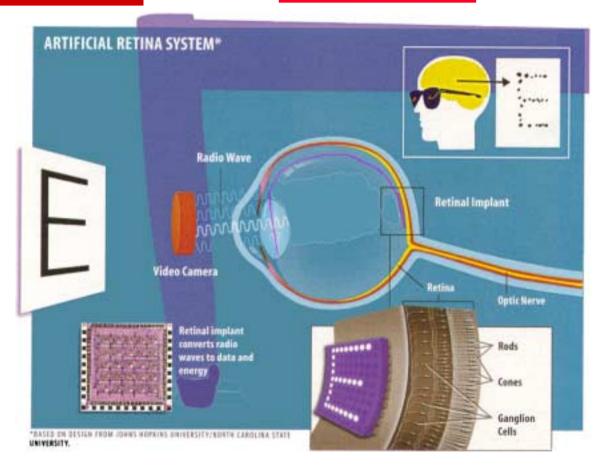

#### **Prosthesis - Dual Intraocular Units**

NC STATE UNIVERSITY

**Retinal Prosthesis**

Courtesy: Prof. Wentai Liu (North Carolina Univ.) http://www.ece.ncsu.edu/erl/faculty/wtl\_data/retina.html

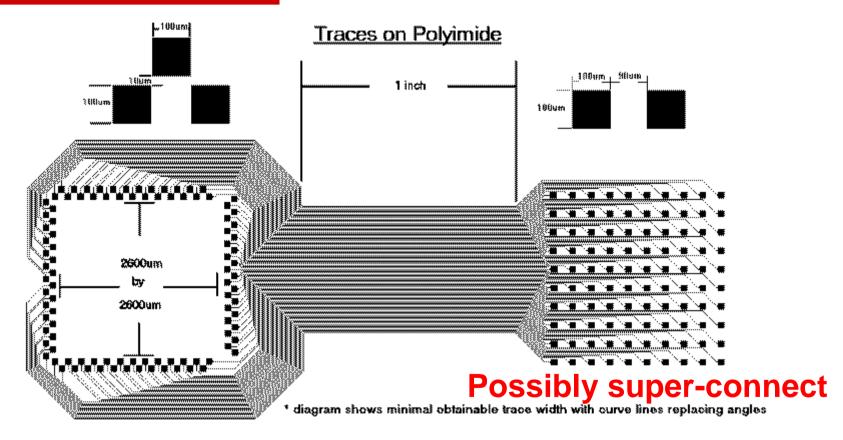

# **Chip + Electrode Array on Polyimide**

#### NC STATE UNIVERSITY

Courtesy: Prof. Wentai Liu (North Carolina Univ.) http://www.ece.ncsu.edu/erl/faculty/wtl\_data/retina.html

# **Super-connect**

P: Power, D: Delay, A: Area, T:Turn-around