# Issues of Current LSI Technology and an Expectation for New System-Level Integration

Takayasu Sakurai

Center for Collaborative Research, and Institute of Industrial Science, University of Tokyo 4-6-1 Komaba, Meguro-ku, Tokyo, Japan, 153-8505 Phone: +81-3-5452-6251 Fax: +81-3-5452-6252 E-mail: tsakurai@iis.u-tokyo.ac.jp http://lowpower.iis.u-tokyo.ac.jp/

## 1. Abstract

Power, interconnection and complexity crises are stringent in designing future deeper submicron LSI's. A new system-level integration using superconnect technology may solve some of the issues related to the current LSI technology. The system-level integration may also open up new application area.

### 2. Scaling and Issues of Current LSI Technology

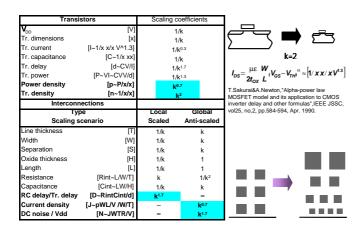

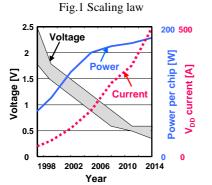

Taking a close look at the scaling law as in Fig.1, we can see that the following three crises are leaning over the LSI technology.

- Power crisis

- Interconnection crisis

- Complexity crisis

The power crisis is depicted in Fig.2. Lower operation voltage naturally increases operation current, which in turn requires thicker metal layers for the current to be distributed throughout the chip without IR-drop. One of the key approaches to low-power design is the memory embedding. By embedding memories, inter-chip communication power can be reduced by two orders of magnitude. The memory embedding, however, is an expensive option, since it increases process steps. A new system-level integration can be a solution to this problem.

As for the interconnection crisis, RC delay increase and IR-drop issue are some of the more stringent issues. Thicker metal layer used in an interposer/package/board may mitigate the problem.

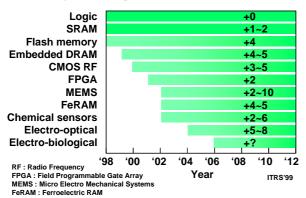

Complexity crisis can only be solved by re-use of the pre-designed blocks and designing at higher abstraction level. Thus, System-on-a-Chip (SoC) where many pre-designed IP's are amalgamated at the higher abstraction is one of the candidates to cope with the complexity crisis. Future electronic systems, however, cannot be built only with the SoC, since many SoC issues have become evident as follows.

- · Huge initial investment for masks & development

- Un-distributed IP's (i.e. CPU, DSP of a certain company)

- IP testability, upfront IP test cost

- Process-dependent memory IP's

- Difficulty in high precision analog IP's due to noise

- Process incompatibility with non-Si materials and/or MEMS

The huge investment in developing the SoC process to embed different kinds of technologies is one of the most vital issues.

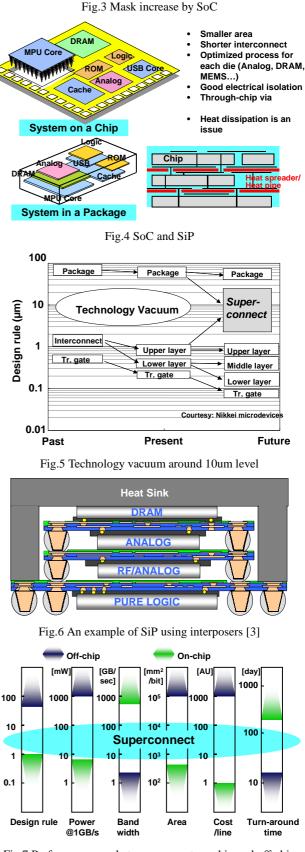

#### 3. System-Level Integration

Recently, however, a new system-level integration called 'superconnect' is attracting attention[1-4], which may solve SoC problems. The superconnect connects separately built and tested chips not by printed circuit boards but rather directly to construct high-performance yet low-cost electronic systems as shown in Fig.4. The superconnect may use around 10 micron level design rules as shown in Fig.5 [4]. Sometimes LSI's in the superconnect are connected in three-dimensional fashion to achieve the higher performance and the smaller geometry. System-in-a-Package (SiP) composed of stacked chips using bonding or interposers as shown in Fig.6 is one realization of the superconnect. The superconnect mitigate IR-drop problems and RC delay problems.

There has been a large gap between on-chip and off-chip interconnects in terms of power, density, performance, cost and turn-around-time as shown in Fig.4. Basically, the large gap comes from the big difference between the design rules of on-chip and off-chip interconnects as shown in Fig.7. It can be said that there is a technology vacuum at present between  $1\mu m$  level on-chip interconnect and  $100\mu m$  level off-chip interconnect will fill the gap between on-chip and off-chip interconnect, making use of  $10\mu m$  level design rule.

Some of the important issues in the future system-level integration are as follows.

- Special design tools for placement & route for co-design of LSI's and assembly

- High-density reliable substrate and metallization technology

low-cost, available known good die (reworkablility and module testing)

#### References

- T.Sakurai, "Superconnect Technology," Trans. C of IEICE, May 2001.

- [2] M.Koyanagi et al., "Neuromorphic Vision Chip Fabricated Using Three-Dimensional Integration Technology," ISSCC Digest of Tech. Papers, pp.270-271, Feb.2001.

- [3] K.Ohsawa, H.Odaira, M.Ohsawa, S.Hirade, T.Iijima, S.G.Pierce, "3-D Assembly Interposer Technology for Next-Generation Integrated Systems," ISSCC Digest of Tech. Papers, pp.272-273, Feb.2001.

- [4] M.Kimura, "Superconnect: 21<sup>st</sup> Century LSI Production and Design Method", Nikkei Microdevices, no.180, pp.62-79, June 2000.

Fig.2 Trend in power and current increase

Fig.7 Performance gap between present on-chip and off-chip connection