Japanese

Power Efficient 3-D integrated VLSI system

3-D integrated VLSI system is power efficient, because it reduces the communication distance by chip stacking. We have proposed and demonstrated several circuits for on-chip sensors, chip-to-chip wireless communications and power delivery/conversion.

Integrated circuits made by organic transistors

Integrated circuits made by organic transistors is studied. Our research team have been developped an artificial skin, sheet type scanners, Braille sheets made by plastic MEMS, power transmission sheet and so on.

Ubiquitous electronics for the people

Ubiquitous electronics for the people

Low-power, high-speed VLSI designs for ubiquitous IT era

- Logic

- New low-power digital circuits, software-hardware cooperative schemes and

low-power digital circuits including leakage current suppression and

adaptive circuits

- Memory

- New memory architectures and circuits operating at less than 0.5V VDD

- Analog

- Ultra short range wireless systems, ultra low-voltage analog circuits

- Wireless superconnect and interconnects in general

- Wireless superconnect to realize 5Gbps/1mW, and analysis of interconnects

for high frequency region

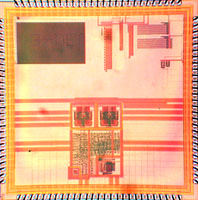

Design of ultra low-power processor

A 0.5-V, 400-MHz, 3.5-mW, 16-bit RISC processor with a 0.25-μm, dual-VTH,

fully-depleted SOI technology was designed.

Experimental results show that the VDD-hopping is effective even in leakage dominant environments.

0.5-V, 400-MHz, 3.5-mW, 16-bit RISC processor

Research on nano-circuits with reduced active leakage

As the silicon VLSI technology reaches nano technology era, it is well-known

that the transistors are getting leaky and power consumption of VLSI tends

to explode. We proposed zigzag super cut-off scheme to reduce leakage power.

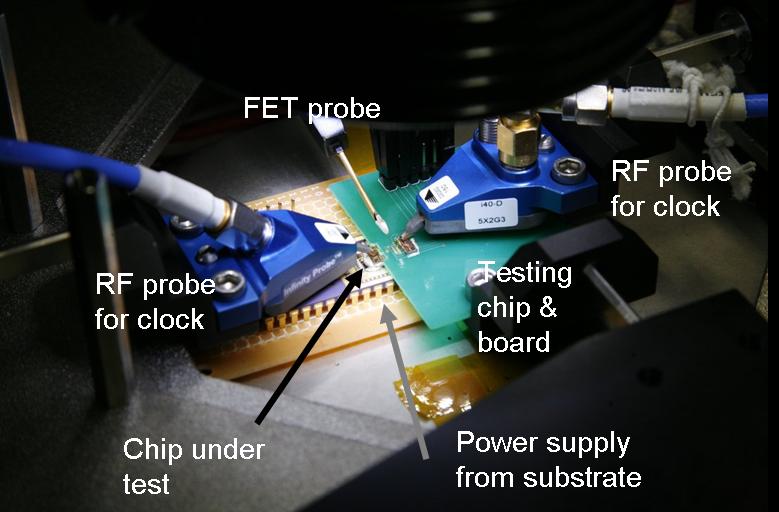

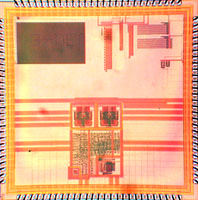

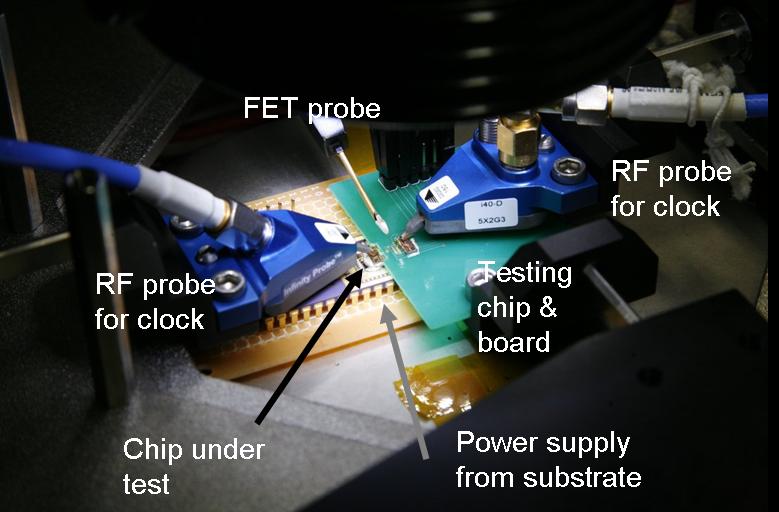

Wireless chip technology for ubiquitous computing

Wireless superconnect is high performance interconnect circuit between chips

required to realize SiP's (System in a Package). In this research topics,

5Gbps/1mW with 20μm2 pad has been realized. We are also working on low-cost

analog circuits and ultra short range wireless circuits.

Deep sub-micron VLSI design

In deep sub-micron designs, signal integrity becomes a big issue. We derived

analytical expressions for coupling noise and delay. Modeling of

interconnects are also pursued.

Embedded system for multimedia applications

Click here for detail

Home