English

低消費電力で高速な三次元VLSIシステム

消費電力を抑える切り札はトランジスタをなるべく密集させて、相互の通信エネルギーを低減することです。そこでチップを三次元積層してトランジスタ密度を上げる三次元積層エコチップが考えられています。桜井研究室は、世界に先駆けて三次元積層チップ間の無線接続を実証して注目され、スーパーコンピュータやテストへの応用がさかんに研究され始めました。最近では無線給電による電力のチップ間伝送の研究も進めています。自分自身の状態を監視し、自分自身で低電力動作点を探してゆく適応型チップの研究も世界をリードしています。

有機トランジスタ集積回路

炭素と水素を基調にした有機トランジスタ回路を研究していて、将来ロボットの電子人工皮膚、曲がった表面からも画像を取り込める光学スキャナ、プラスチックMEMS(マイクロマシン)と組み合わせたシート型点字シート、コードがなくてもパソコンや携帯が動く無線電力伝送シート、置けばつながる通信シートなどの研究を行ってきました。これらのシリコンなどの無機材料とプラスチックなどの有機材料を組み合わせた融合型の集積回路は新しい可能性を拓きますが、世界でも例を見ない当研究室の成果に注目が集まっています。

人々の生活に溶け込むVLSI

半導体チップは現代の情報社会の基幹技術となっています。しかし近年、物理的な世界にも応用が始まっています。環境全般、野山、街角、交通機関、ホーム、人体などにも半導体チップが入り込み安心・安全・豊かな生活を支えるために人々の生活に浸透してゆこうとしています。このように膨大な数のチップが使われ始めたので、今まで以上に低電力性が求められるとともに、新しいチャレンジが一杯でてきました。これらの新天地では、新しいVLSI設計の考え方が必要となっています。

ユビキタスIT時代の低消費電力・高速LSI設計

- ロジック

- 超低電圧時代に対応したアクティブ時のリーク電力の低減新方式、ソフトウェア、低電力FPGA

- メモリ

- 0.5V以下の電源電圧を想定したメモリ

- アナログ

- 極短距離ワイヤレス回路、超低電圧アナログ回路

- ワイヤレススーパーコネクト・配線

- 5Gbps/1mWのデータレートを実現するワイヤレススーパーコネクト、高周波の配線特性解析・評価

超低電力プロセッサの設計

電源電圧0.5Vという低電圧下において400MHzで動作するプロセッサを設計し、0.25μm、デュアルVTH、完全空乏型SOI技術を使って検証し、0.5V世代のVLSI設計の一つの方向性を示した。またソフトウェアと協調して低電力化を達成するVDDホッピングはリークが支配的な環境においても有効であることを示した。

0.5-V, 400-MHz, 3.5-mW, 16-bit RISCプロセッサ

アクティブリークを削減するナノサーキットの研究

MOSデバイス寸法がナノ領域に入るに従ってリーク電流が増加し、動作時でさえ支配的になってくることをつきとめた。リーク電力低減化への統括的設計手法などの設計指針を確立するとともに、リーク電力をカットオフ制御するzigzag方式の提案、実証を行った。

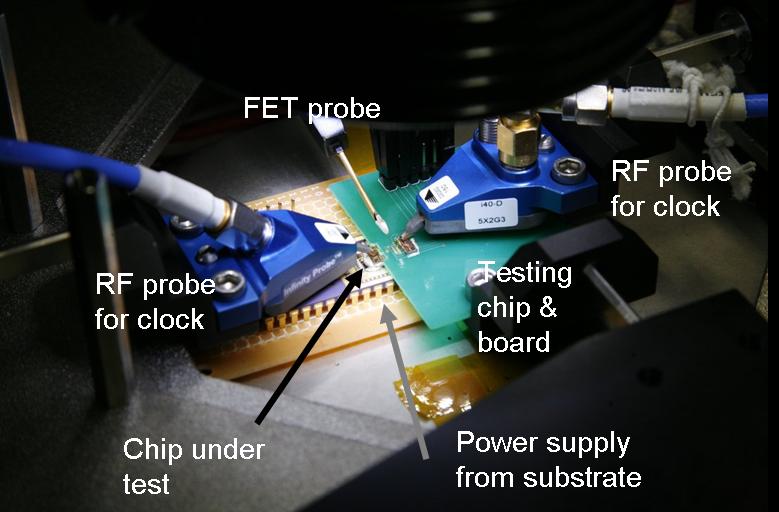

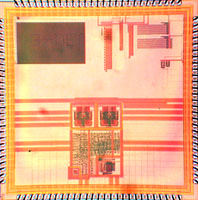

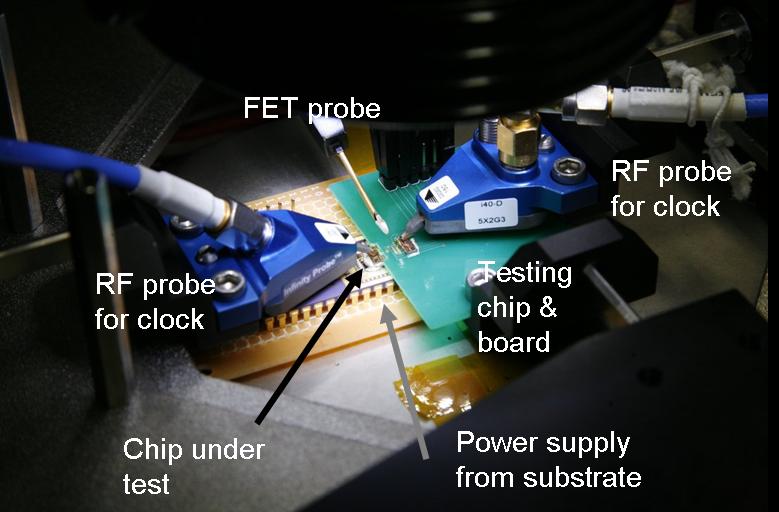

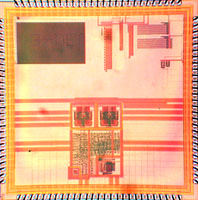

ユビキタスコンピューティングに対応した無線チップ技術

電子システムの複雑化に伴い、プロセッサとメモリLSIあるいはサブシステムLSIなどLSI間接続の高速大容量化が進み、「スーパーコネクト(チップの高性能接続)」が必要となっている。本研究では、20μm角のパッドで5Gbps/1mWを実現し、将来の新しいシステム実装方法に道を開いた。また、低コストのアナログ回路や極短距離ワイヤレス回路の提案を行っている。

ディープサブミクロンVLSI設計

ディープサブミクロン世代の設計はシグナルインテグリティ(信号の確かさ)の問題の解決が重要である。配線のカップリングノイズ、遅延を正確に見積り、モデル化を行い設計の指針を作る。

マルチメディアアプリケーション向け組み込みシステム

研究内容の概要スライドはこちら

システムLSIの低消費電力化に興味のある方は以下の「低消費電力・高速LSI技術懇談会」をご参照ください。

21世紀をリードする切り札:

超省エネLSIをデバイスプロセスと回路システムから築く

- ■低消費電力・高速LSI技術懇談会(RC-12)

- ■代表幹事:

- 桜井貴康 (東京大学 国際・産学共同研究センター 教授)

- 平本俊郎 (東京大学 生産技術研究所 教授)

- 黒田忠広 (慶應義塾大学 理工学部電子工学科 教授)

-

http://www.iis.u-tokyo.ac.jp/shourei/rc2003/rc12-2003.html

Home